# Microwave Circuit Design

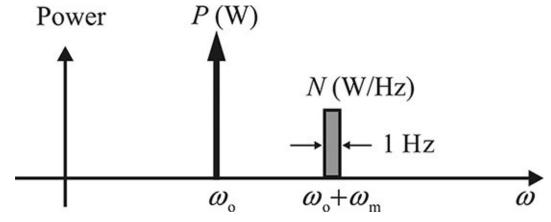

A Practical Approach

KYUNG-WHAN YEOM

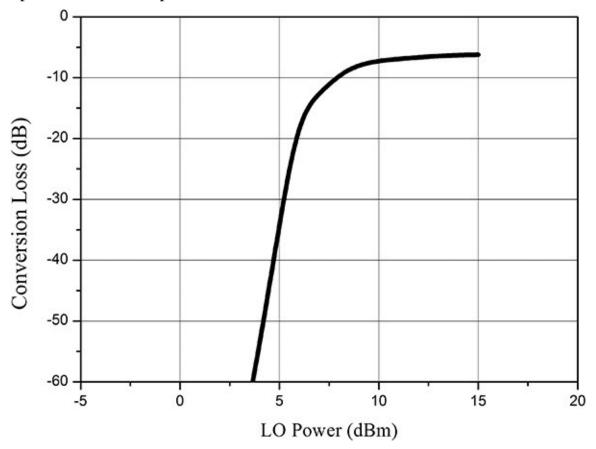

#### **About This eBook**

ePUB is an open, industry-standard format for eBooks. However, support of ePUB and its many features varies across reading devices and applications. Use your device or app settings to customize the presentation to your liking. Settings that you can customize often include font, font size, single or double column, landscape or portrait mode, and figures that you can click or tap to enlarge. For additional information about the settings and features on your reading device or app, visit the device manufacturer's Web site.

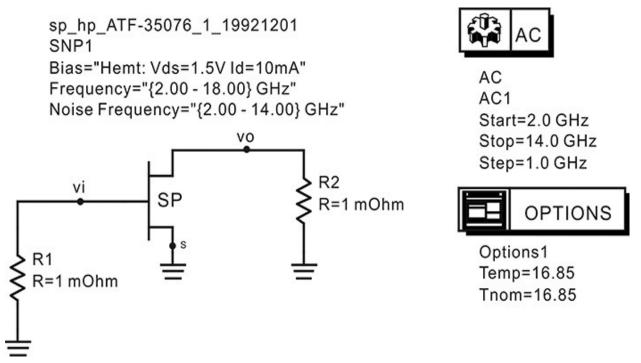

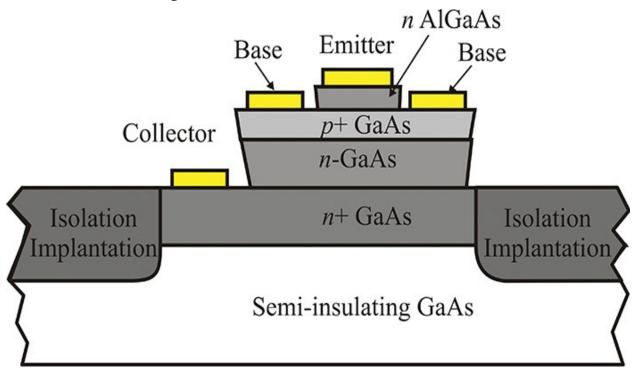

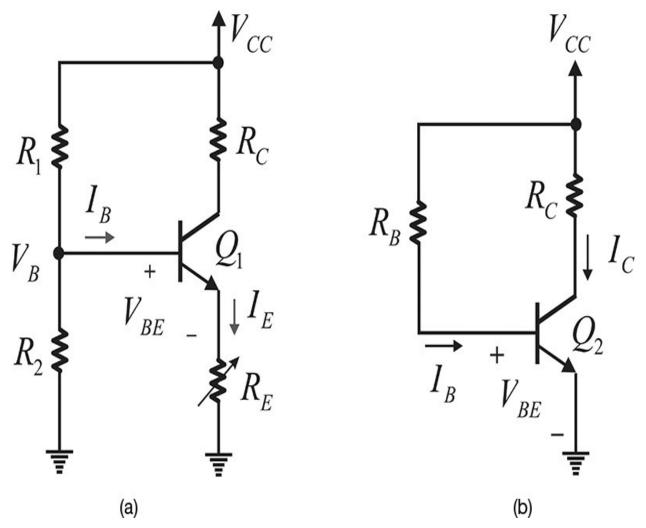

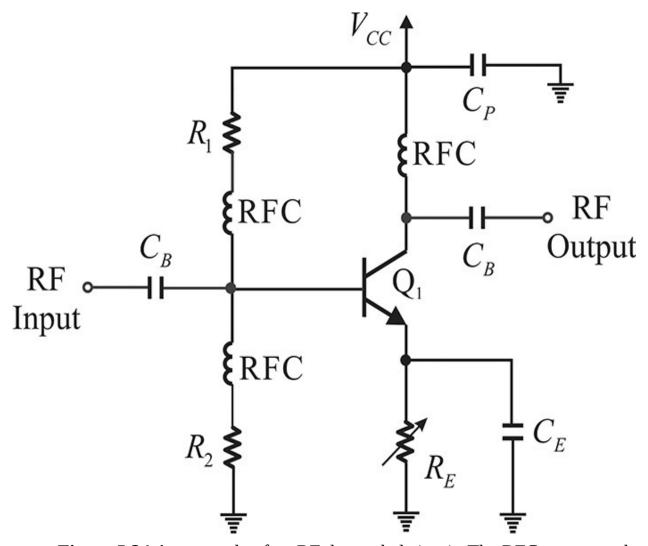

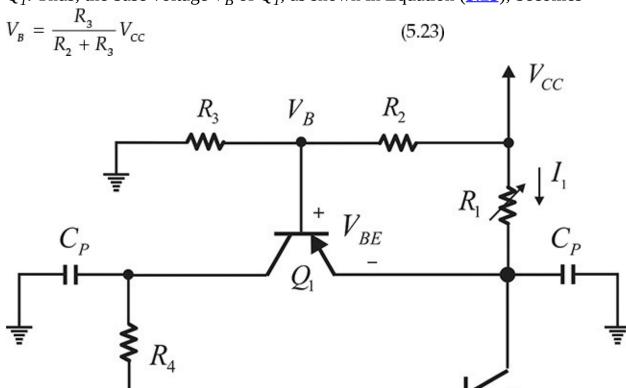

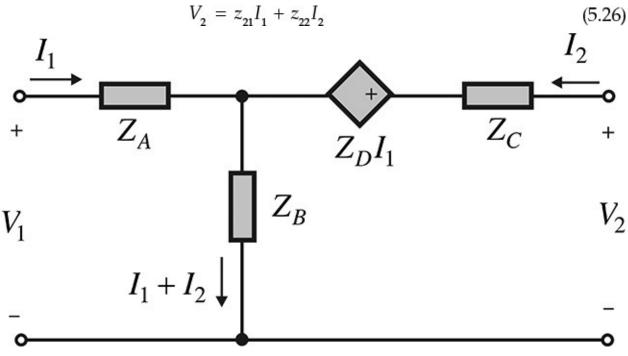

Many titles include programming code or configuration examples. To optimize the presentation of these elements, view the eBook in single-column, landscape mode and adjust the font size to the smallest setting. In addition to presenting code and configurations in the reflowable text format, we have included images of the code that mimic the presentation found in the print book; therefore, where the reflowable format may compromise the presentation of the code listing, you will see a "Click here to view code image" link. Click the link to view the print-fidelity code image. To return to the previous page viewed, click the Back button on your device or app.

# **Microwave Circuit Design**

## A Practical Approach Using ADS

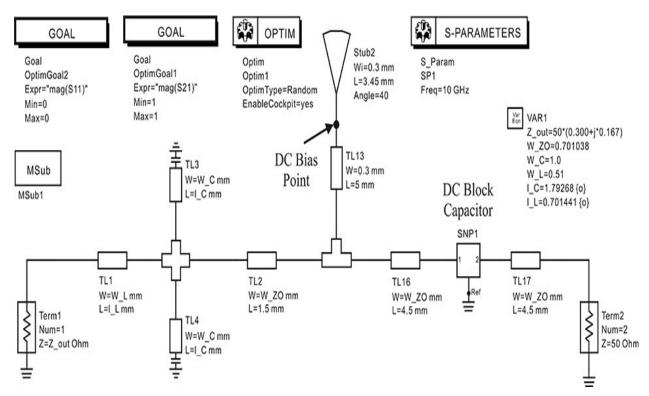

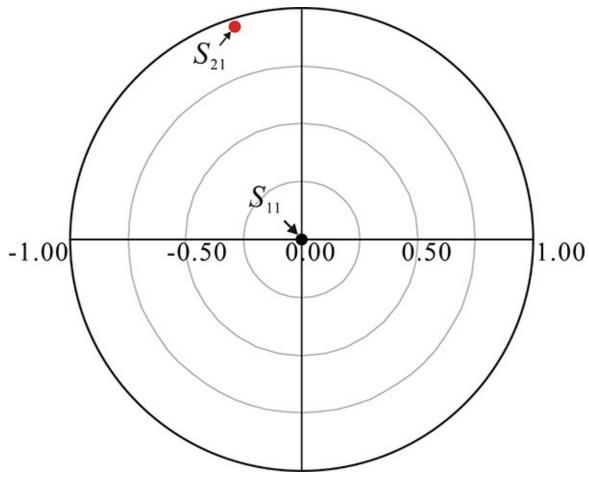

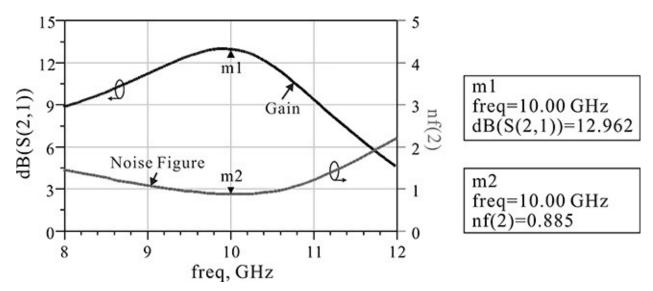

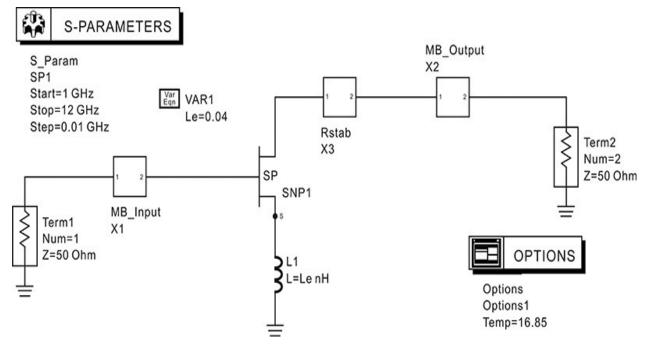

**Kyung-Whan Yeom**

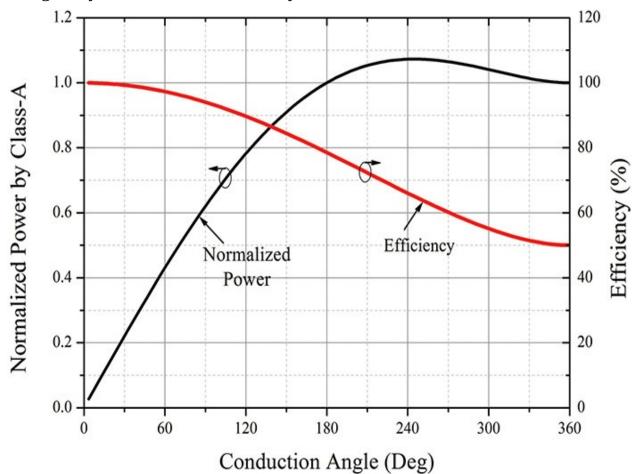

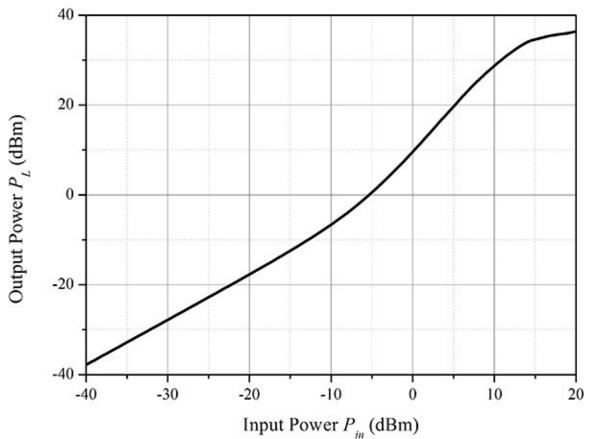

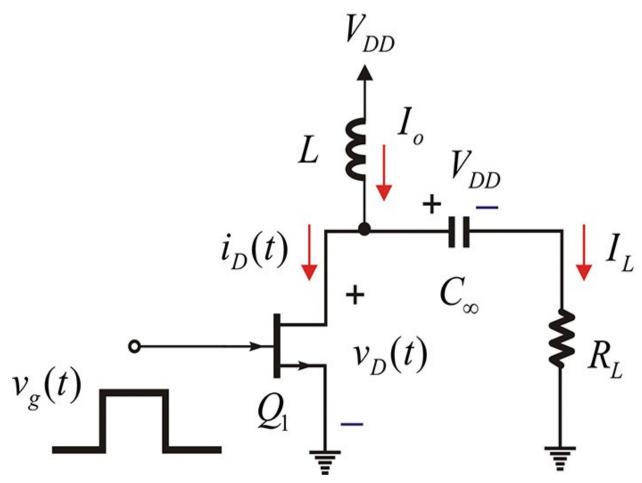

New York • Boston • Indianapolis • San Francisco Toronto • Montreal • London • Munich • Paris • Madrid Capetown • Sydney • Tokyo • Singapore • Mexico City

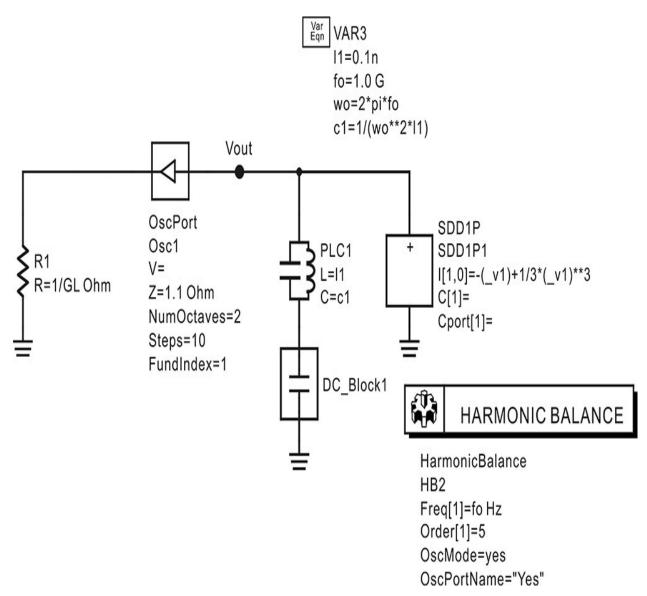

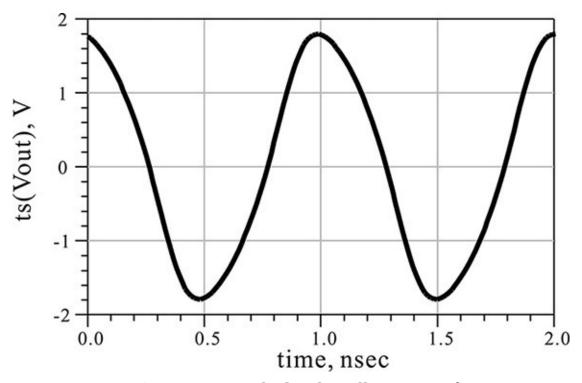

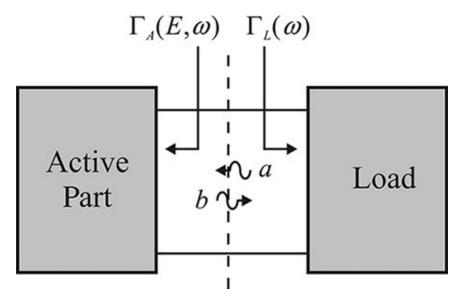

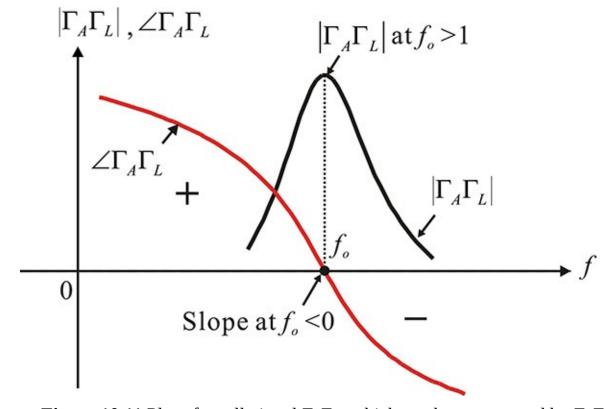

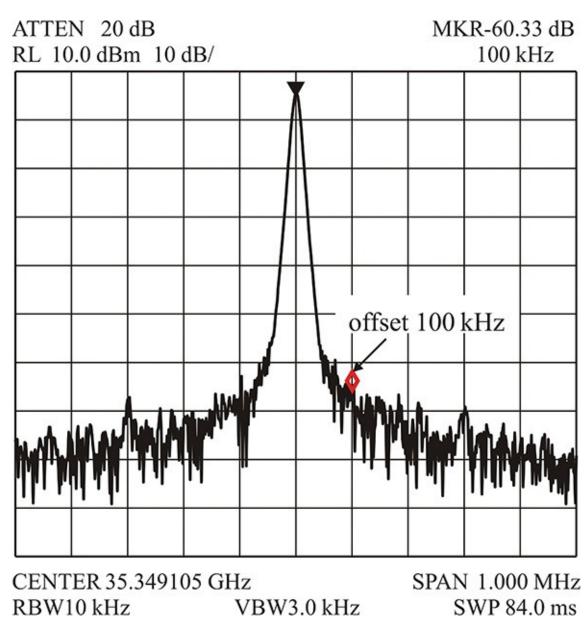

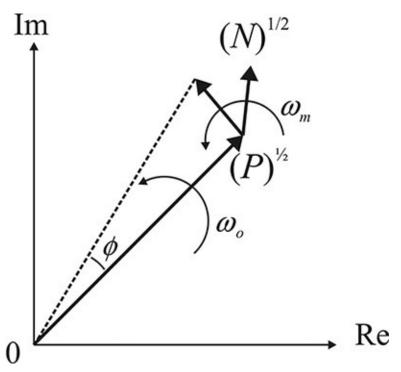

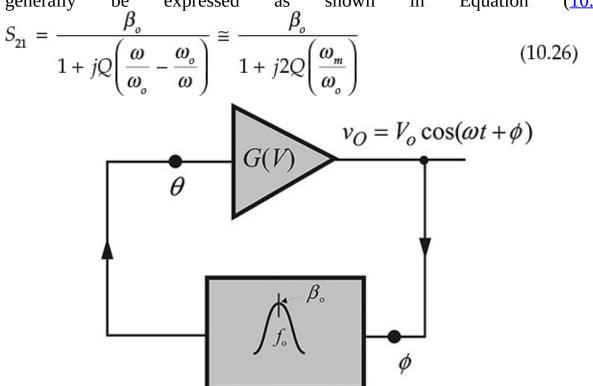

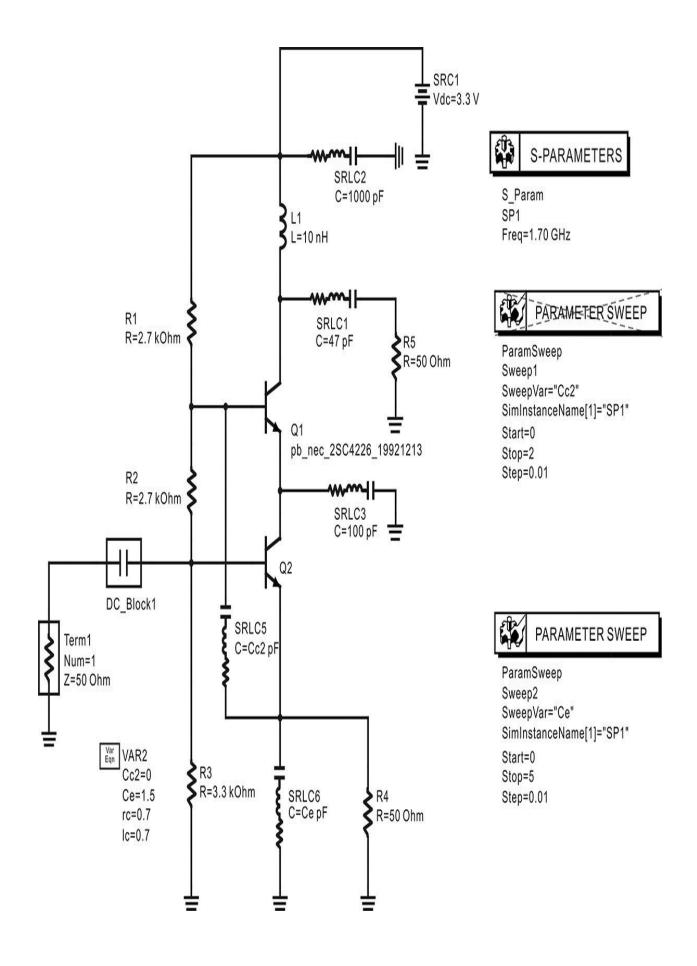

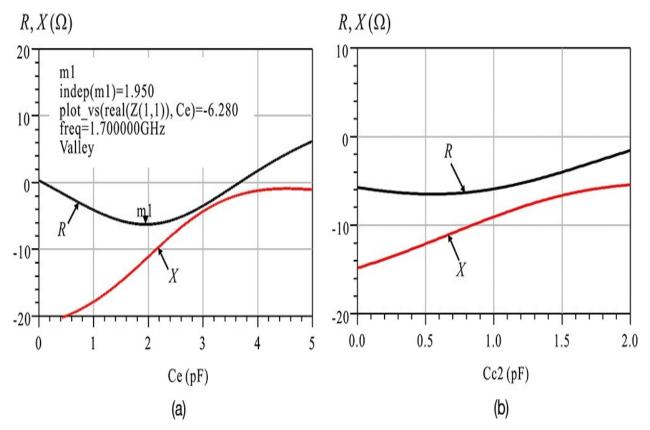

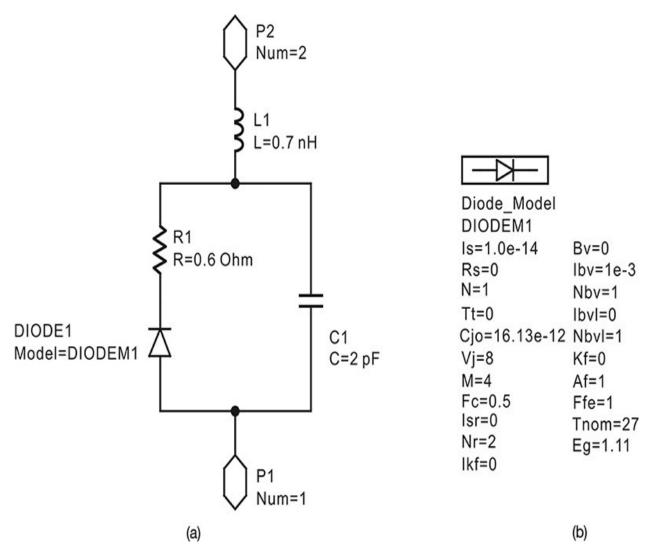

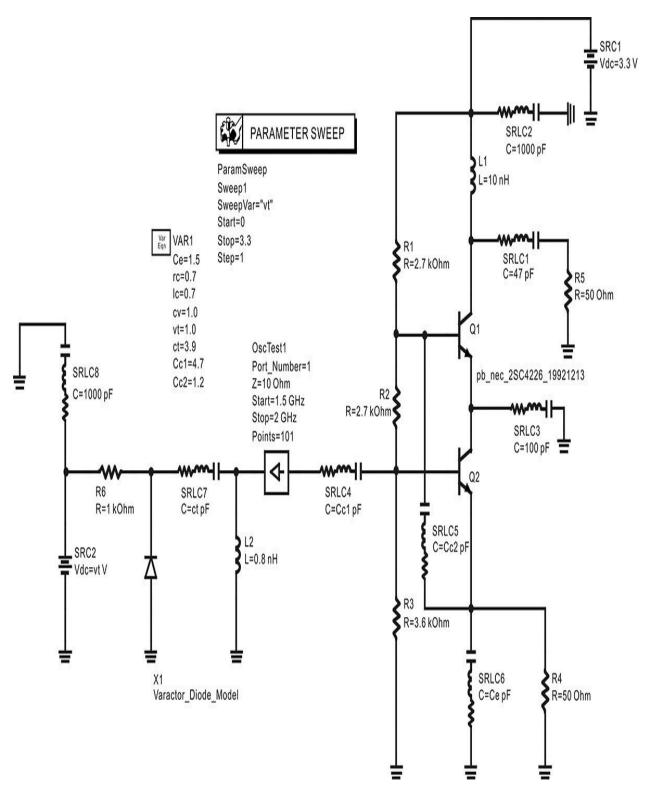

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals.

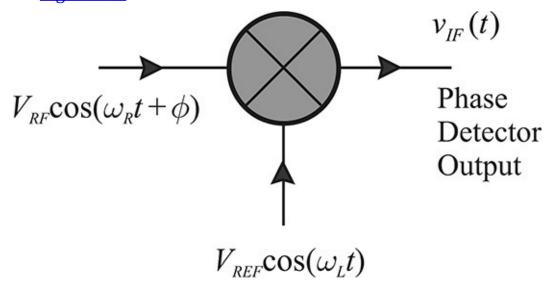

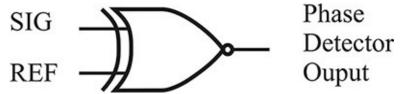

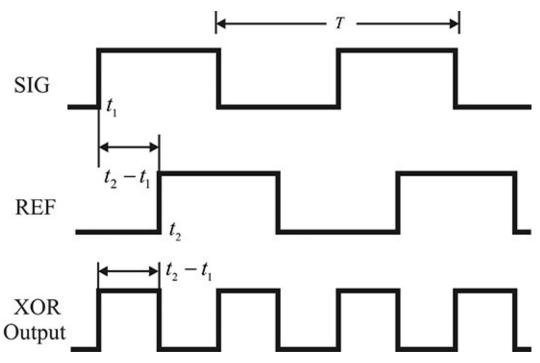

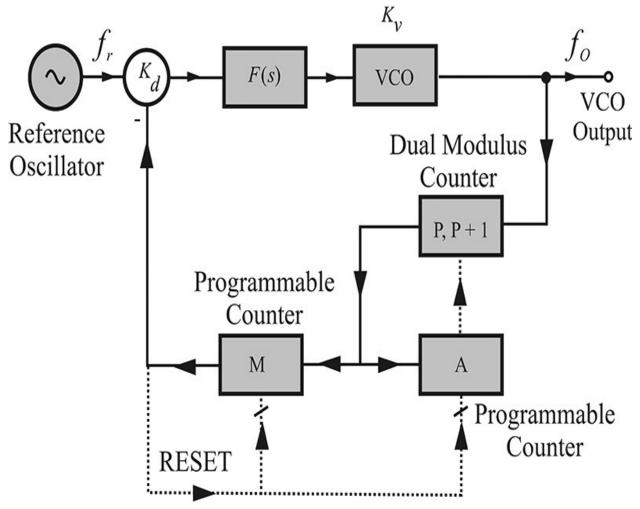

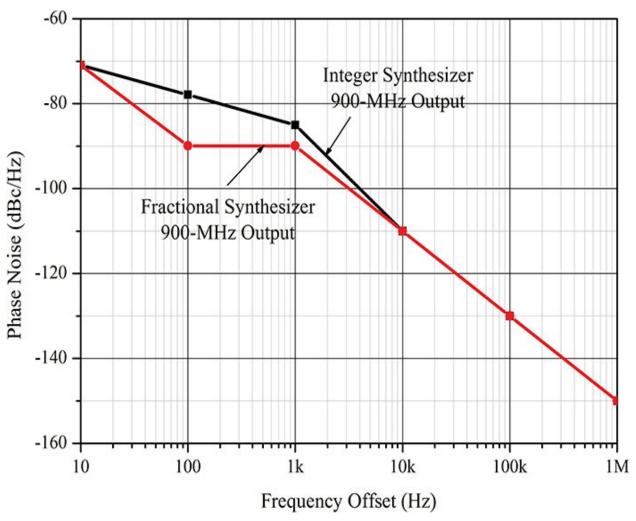

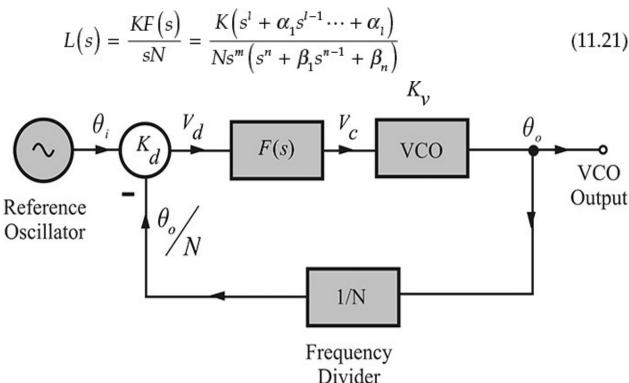

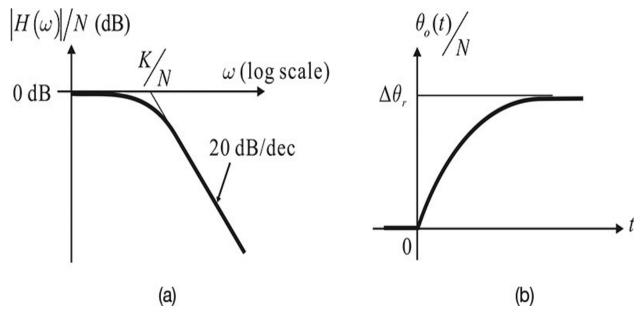

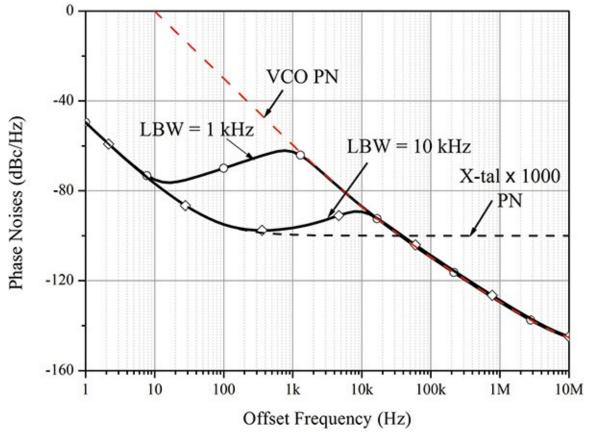

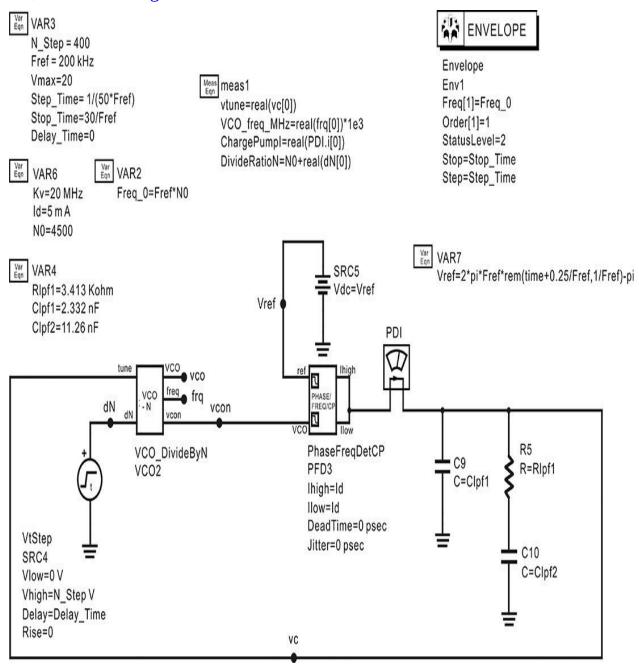

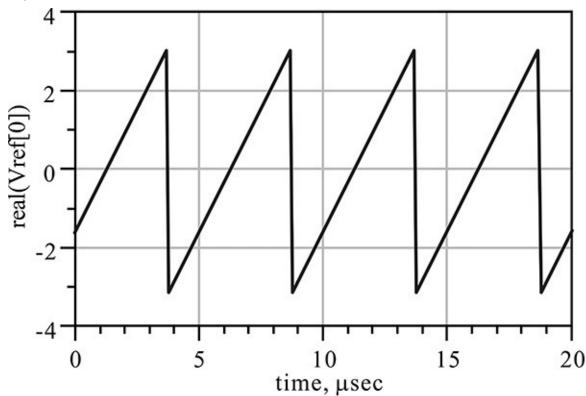

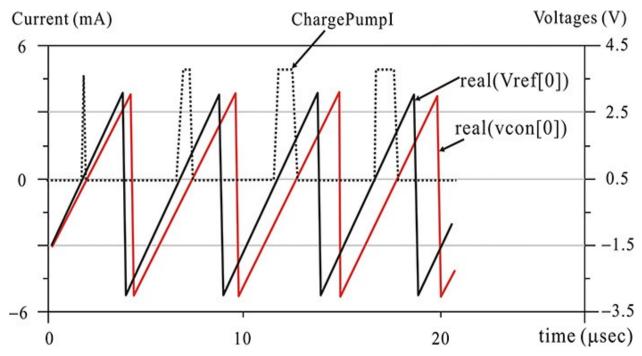

The author and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

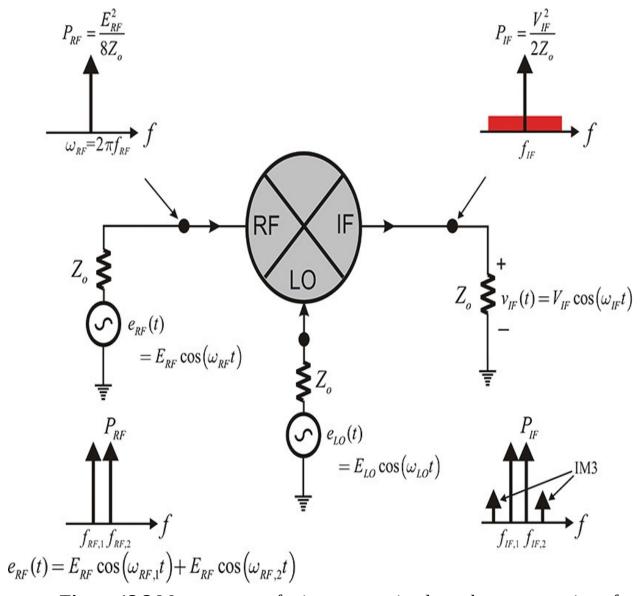

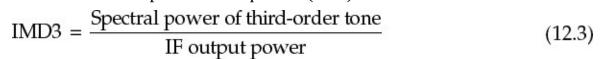

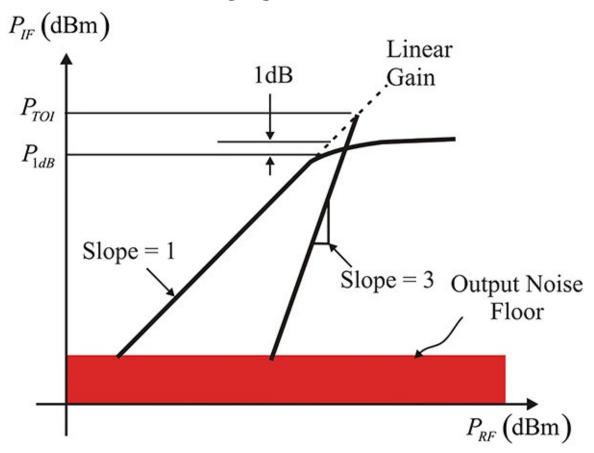

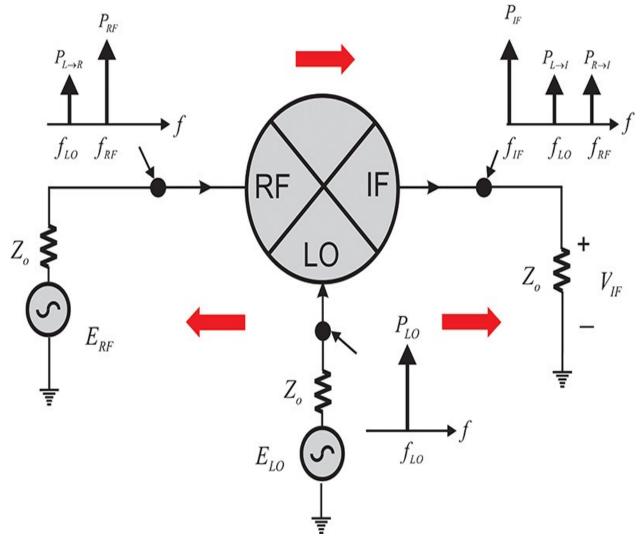

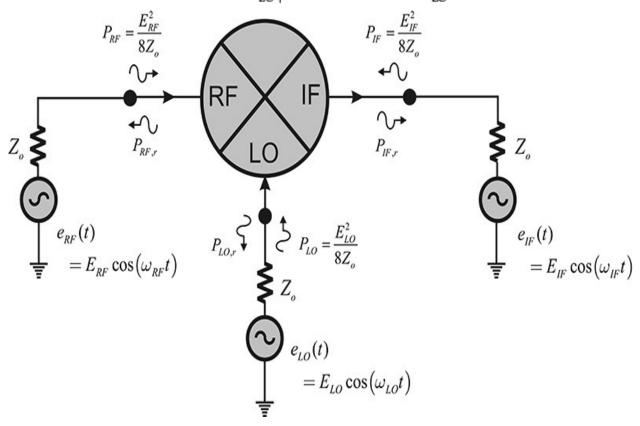

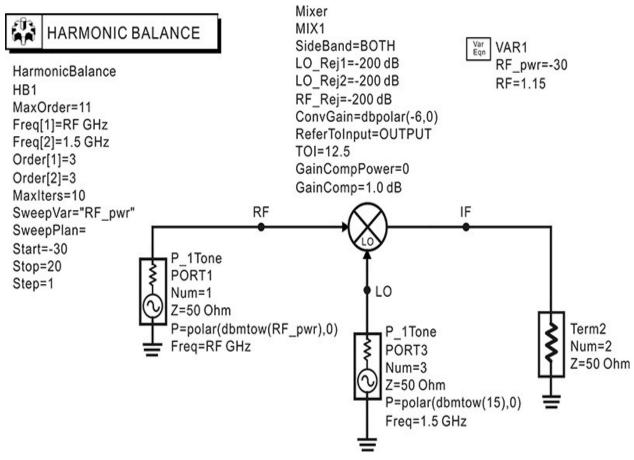

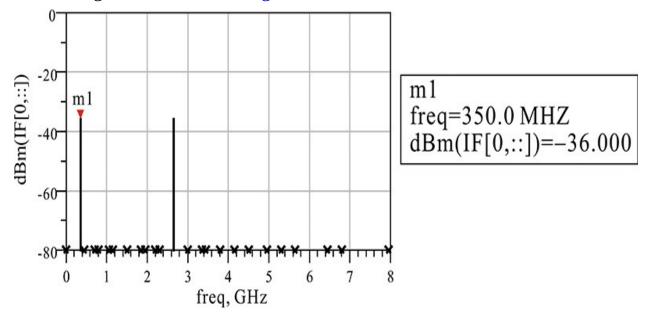

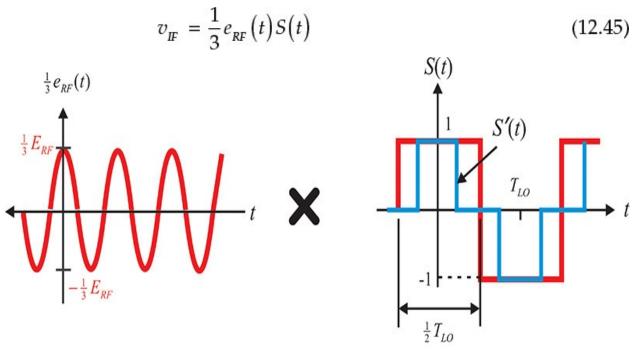

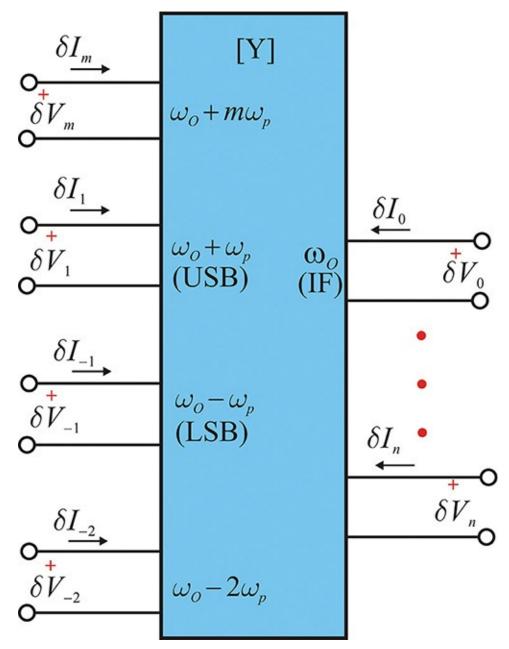

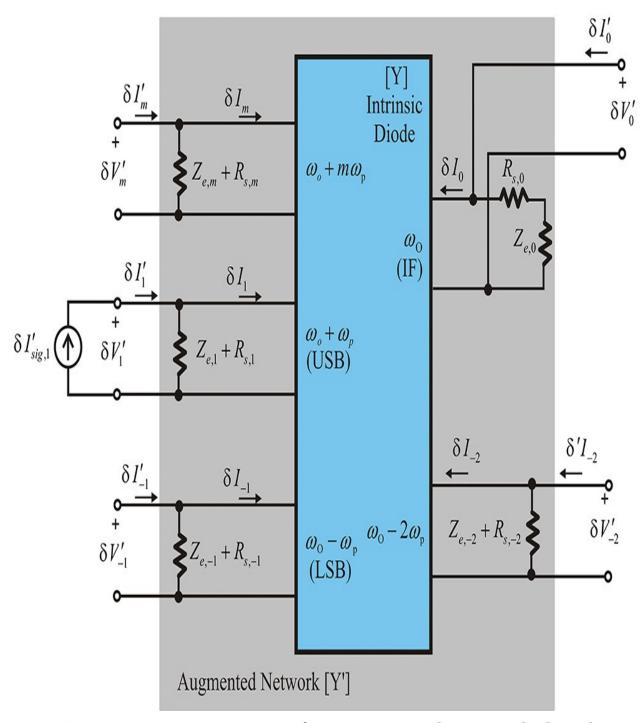

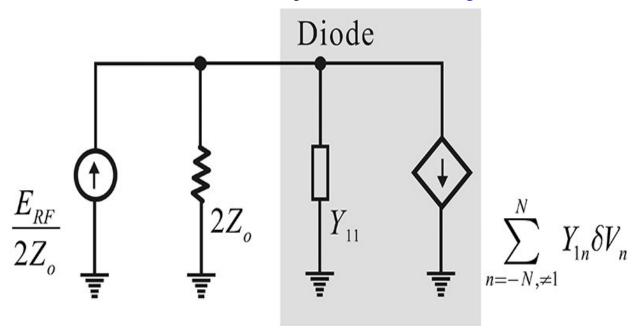

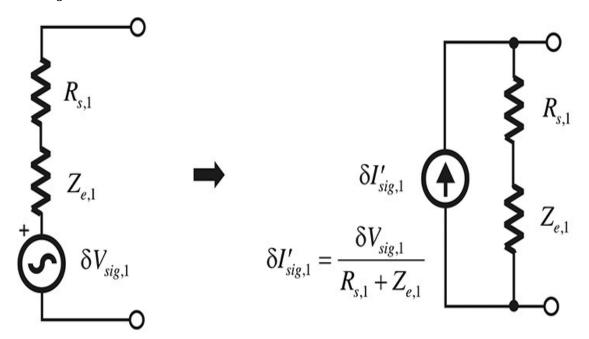

For information about buying this title in bulk quantities, or for special sales opportunities (which may include electronic versions; custom cover designs; and content particular to your business, training goals, marketing focus, or branding interests), please contact our corporate sales department at <a href="mailto:corpsales@pearsoned.com">corpsales@pearsoned.com</a> or (800) 382-3419.

For government sales inquiries, please contact governmentsales@pearsoned.com.

For questions about sales outside the United States, please contact <a href="mailto:international@pearsoned.com">international@pearsoned.com</a>.

Visit us on the Web: <a href="mailto:informit.com/ph">informit.com/ph</a>

Library of Congress Cataloging-in-Publication Data

Yeom, Kyung-Whan.

Microwave circuit design : a practical approach using ADS / Kyung-Whan Yeom.

pages cm

Includes index.

ISBN 978-0-13408678-1 (hardcover : alk. paper)—ISBN 0-13-408678-3

1. Microwave circuits—Computer-aided design. 2. Advanced design system. I. Title.

TK7876.Y46 2015 621.381'32—dc23

20150041

Copyright © 2015 Pearson Education, Inc.

ADS (Advanced Design System) is a trademark of Keysight Technologies. HFSS (High Frequency Structure Simulator) is a trademark of ANSYS, Inc. Mathcad is a trademark of PTC Inc. Keysight Technologies, Inc. makes no warranty as to the accuracy or completeness of the foregoing material and hereby disclaims any responsibility therefor. Copyright 2000–2014 Keysight Technologies, Inc. Reproduced with permission.

All rights reserved. Printed in the United States of America. This publication is protected by copyright, and permission must be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. To obtain permission to use material from this work, please submit a written request to Pearson Education, Inc., Permissions Department, 200 Old Tappan Road, Old Tappan, New Jersey 07675, or you may fax your request to (201) 236-3290.

ISBN-13: 978-0-13408678-1

ISBN-10: 0-13-408678-3

Text printed in the United States on recycled paper at Edwards Brothers Malloy in Ann Arbor, Michigan.

First printing May, 2015

To my wife Cho Soon-Duk (조순덕) and son Yeom Jae-Hyung (염재형)

## **Contents**

| <u>Preface</u>                                      |

|-----------------------------------------------------|

| <u>Acknowledgments</u>                              |

| About the Author                                    |

| <b>Chapter 1 Microwave Integrated Circuits</b>      |

| 1.1 Classification of Microwave Integrated Circuits |

| 1.2 Microwave Circuits in a Communication System    |

| 1.3 Summary                                         |

| <b>Chapter 2 Passive Devices</b>                    |

| 2.1 Impedances                                      |

| 2.2 Classification                                  |

| 2.3 Equivalent Circuits                             |

| 2.3.1 Chip-Type Capacitors                          |

| 2.3.2 Chip-Type Inductors                           |

| 2.3.3 Chip-Type Resistors                           |

| 2.4 Impedance Measurements                          |

| 2.5 Summary                                         |

| <b>Chapter 3 Transmission Lines</b>                 |

| 3.1 Introduction                                    |

| 3.2 Parameters                                      |

| 3.2.1 Phase Velocity                                |

| 3.2.2 Wavelength                                    |

| 3.2.3 Characteristic Impedance                      |

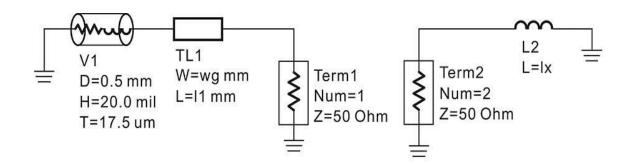

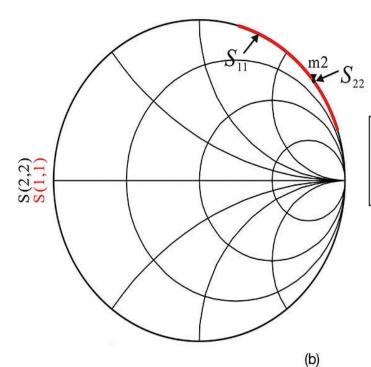

| 3.2.4 Measurements                                  |

| 3.3 Coaxial and Microstrip Lines                    |

| 3.3.1 Coaxial Line                                  |

| 3.3.2 Microstrip Line                               |

| 3.4 Sinusoidal Responses                         |

|--------------------------------------------------|

| 3.4.1 Phasor Analysis                            |

| 3.4.2 Reflection and Return Loss                 |

| 3.4.3 Voltage Standing Wave Ratio (VSWR)         |

| 3.4.4 Smith Chart and Polar Chart                |

| 3.5 Applications                                 |

| 3.5.1 Short-Length Transmission Line             |

| 3.5.2 Resonant Transmission Line                 |

| 3.5.3 Two-Port Circuit Application               |

| 3.6 Discontinuities                              |

| 3.6.1 Open-End Microstrip                        |

| 3.6.2 Step and Corner Discontinuities            |

| 3.6.3 T-Junction and Cross Junction              |

| 3.7 Summary                                      |

| Chapter 4 S-parameters and Noise Parameters      |

| 4.1 S-parameters                                 |

| 4.1.1 Voltage S-Parameter Definition             |

| 4.1.2 Definitions and Properties of S-Parameters |

| 4.1.3 Ports and S-Parameter Simulation           |

| 4.1.4 S-Parameter Conversion                     |

| 4.1.5 Shift of Reference Planes                  |

| 4.1.6 Insertion Loss and Return Loss             |

| 4.1.7 Input Reflection Coefficient               |

| 4.2 Noise Parameters                             |

| 4.2.1 Expression of Internal Noise               |

| 4.2.2 Representation of Noise Signals            |

| <u>4.2.3 Noise Figure</u>                        |

| 4.2.4 Expression of Noise Parameters             |

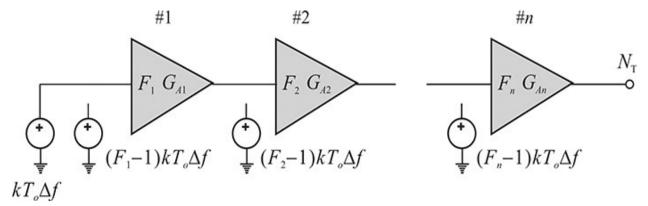

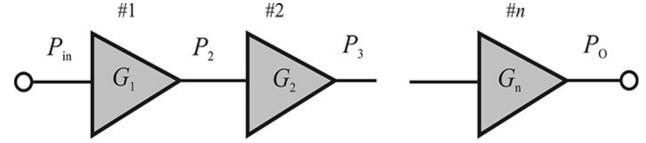

| <u>4.2.5 Frii's Formula</u>                      |

|                                                  |

```

4.2.6 Measurement of Noise Figure and Noise Parameters

4.3 File Formats

4.4 Summary

Chapter 5 Introduction to Microwave Active Devices

5.1 Introduction

5.2 Field Effect Transistor (FET)

5.2.1 GaAs MESFET

5.2.2 Large-Signal Equivalent Circuit

5.2.3 Simplified Small-Signal Equivalent Circuit and S-

Parameters

5.2.4 Package

5.2.5 GaAs pHEMT

5.3 Bipolar Junction Transistor (BJT)

5.3.1 Operation of an Si BJT

5.3.2 Large-Signal Model of a BJT

5.3.3 Simplified Equivalent Circuit and S-Parameters

5.3.4 Package

5.3.5 GaAs/AlGaAs HBT

5.4 DC-Bias Circuits

5.4.1 BJT DC-Bias Circuits

5.4.2 FET DC-Bias Circuit Design

5.4.3 S-Parameter Simulation

5.5 Extraction of Equivalent Circuits

5.6 Summary

Chapter 6 Impedance Matching

6.1 Introduction

6.2 Maximum Power Transfer Theorem

6.3 Discrete Matching Circuits

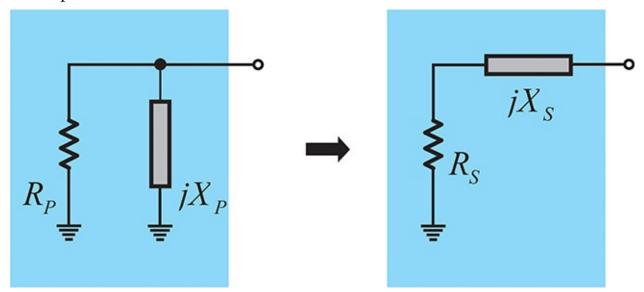

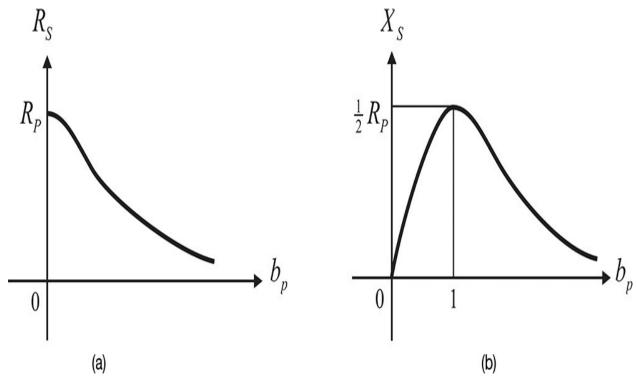

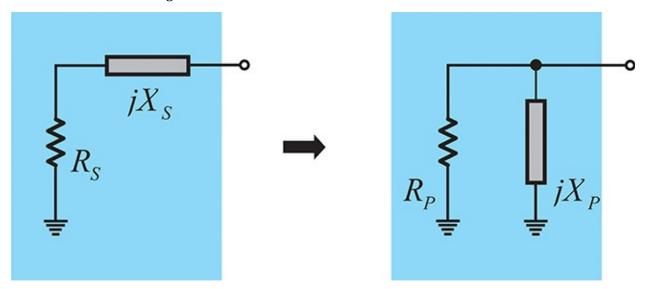

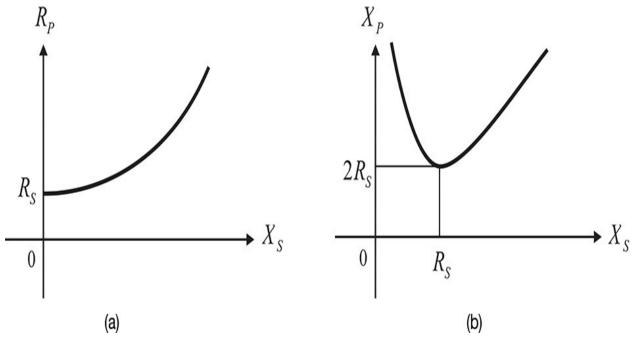

6.3.1 Series-to-Parallel Conversion

```

```

6.3.2 L-Type Matching Circuit

6.3.3 A \pi-Type Matching Circuit

6.3.4 T-Type Matching Circuit

6.3.5 Double L-Type Matching Circuit

6.3.6 Matching Circuit Design for a General Source

Impedance

6.4 Transmission-Line Matching Circuits

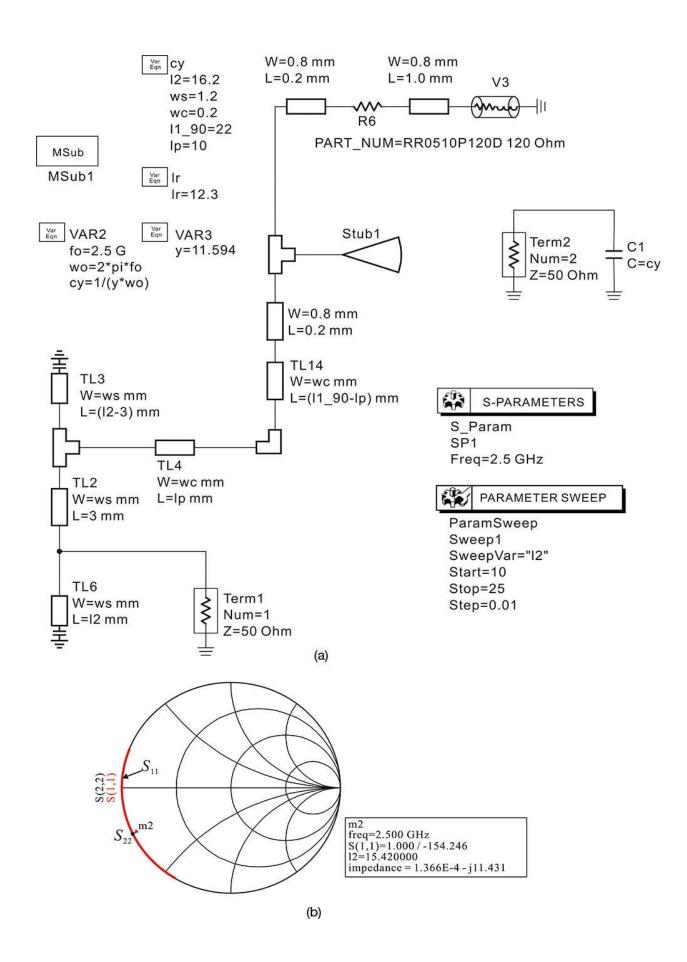

6.4.1 Single-Stub Tuner

6.4.2 Impedance Inverter

6.5 Summary

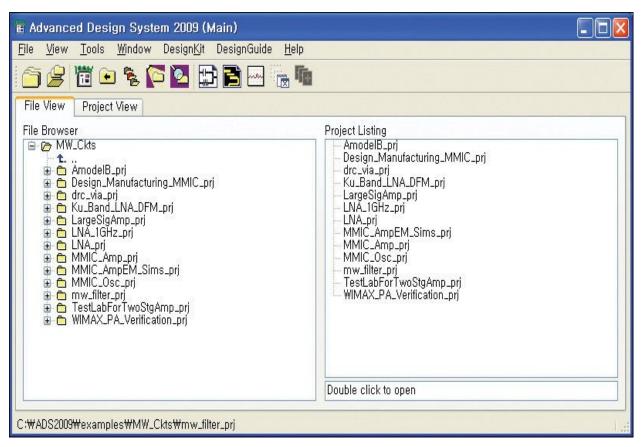

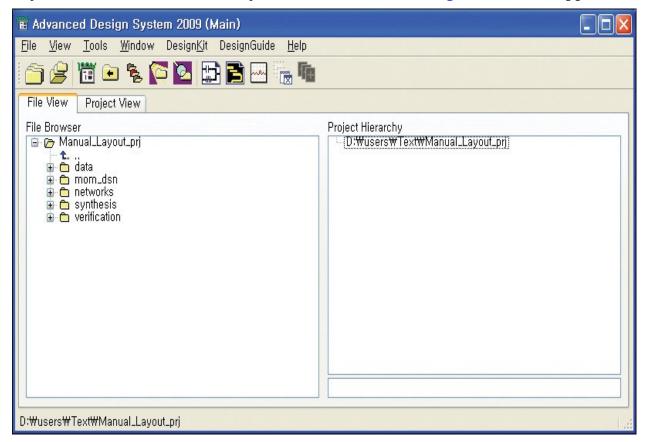

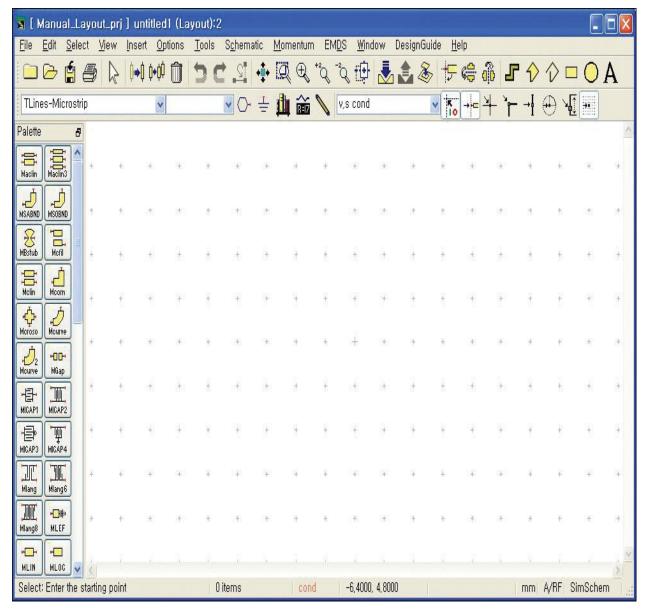

Chapter 7 Simulation and Layout

7.1 Simulation in ADS

7.2 Circuit Simulations

7.2.1 Classification of Circuit Simulations

7.2.2 DC Simulation

7.2.3 Transient Simulation

7.2.4 AC Simulation

7.2.5 Harmonic Balance Simulation

7.2.6 Multi-Tone Harmonic Balance

7.2.7 Optimization

7.3 Layout

7.3.1 Layout Example

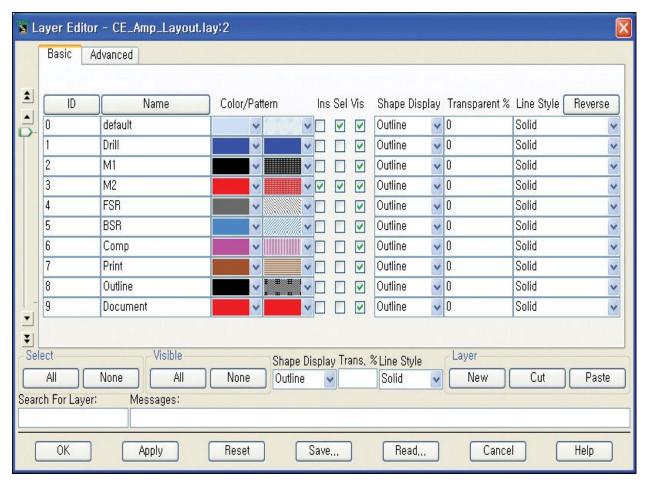

7.3.2 Layer Preparation for Layout

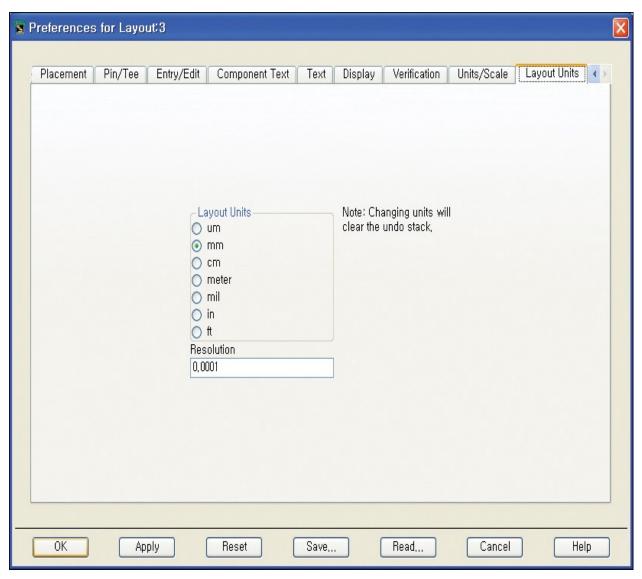

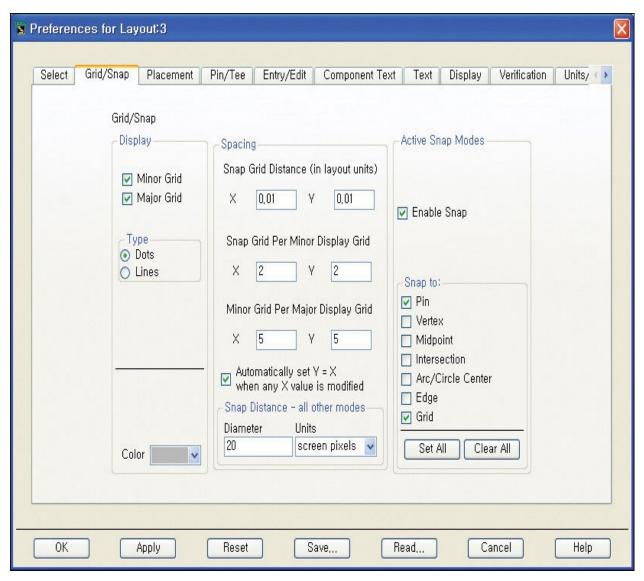

7.3.3 Layout Units and Grid Set

7.3.4 Outline Setting

7.3.5 Component Layout

7.3.6 Layout Using Components

7.4 Momentum

7.4.1 Theory

```

| 7.4.2 Settings and EM Simulation                             |

|--------------------------------------------------------------|

| 7.5 Summary                                                  |

| Chapter 8 Low-Noise Amplifiers                               |

| 8.1 Introduction                                             |

| <b>8.2 Gains</b>                                             |

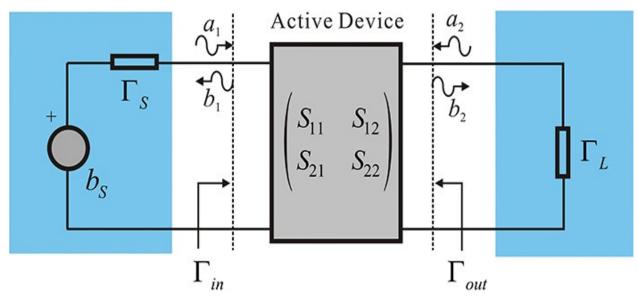

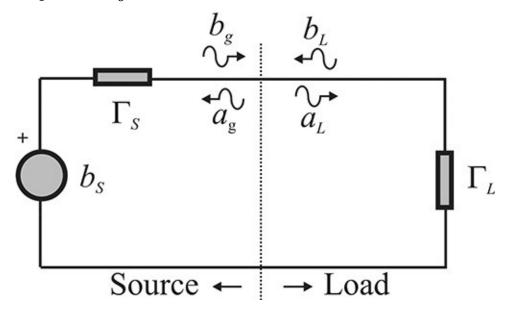

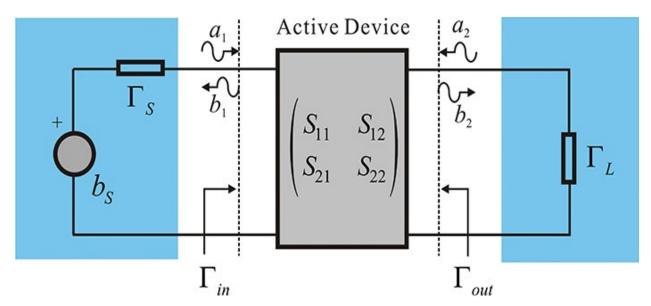

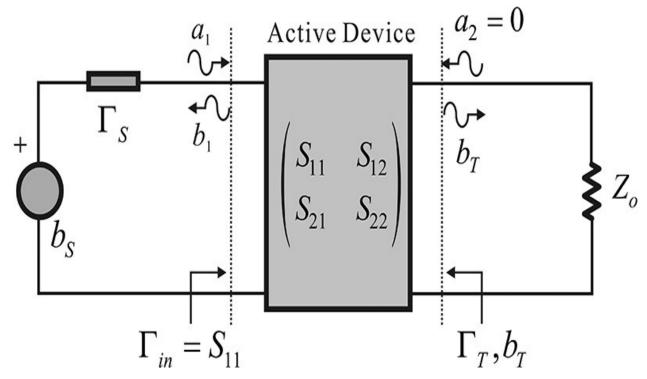

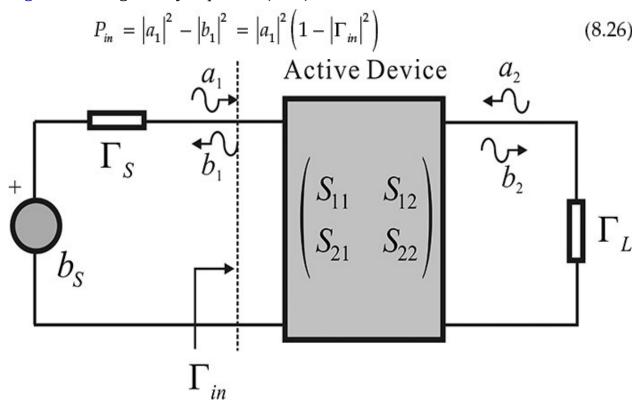

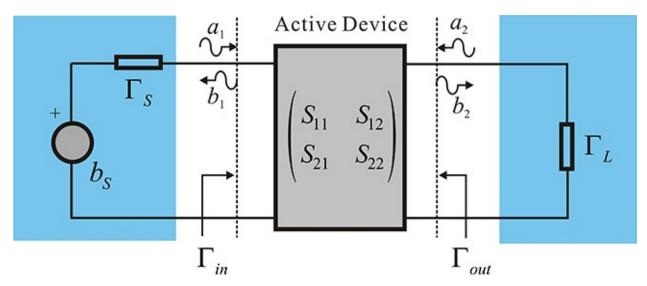

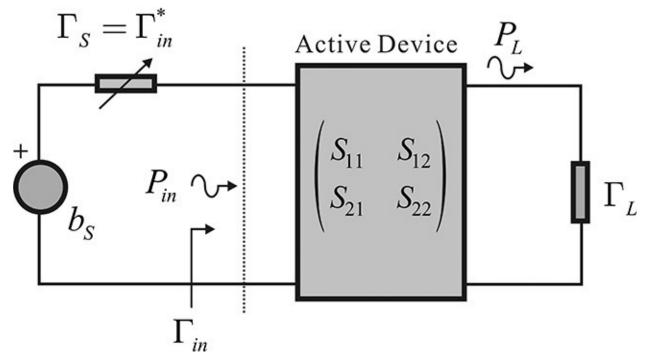

| 8.2.1 Definition of Input and Output Reflection Coefficients |

| 8.2.2 Thevenin Equivalent Circuit                            |

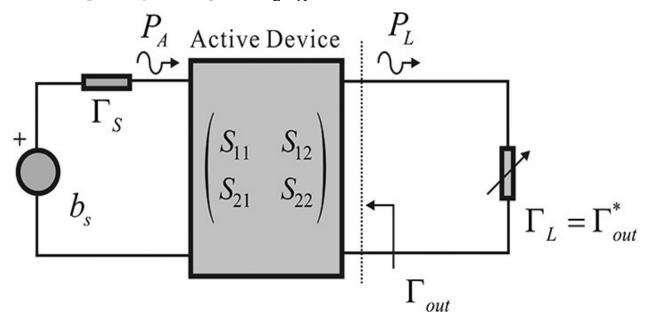

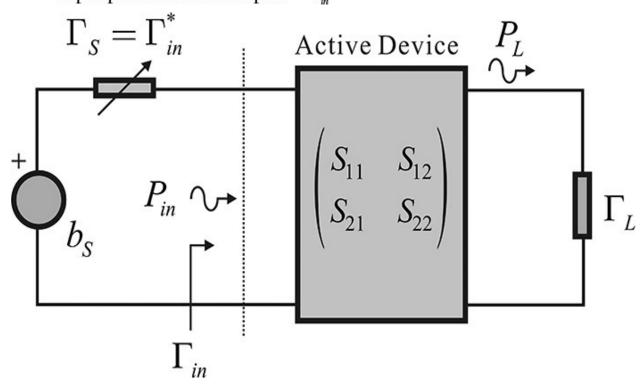

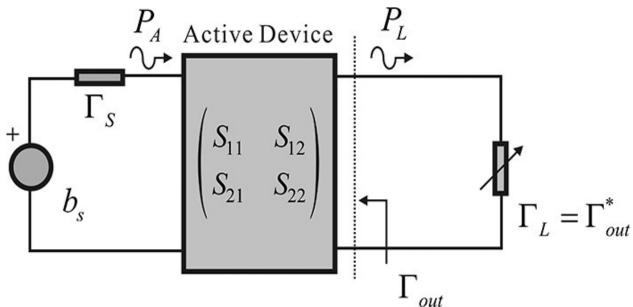

| 8.2.3 Power Gains                                            |

| 8.3 Stability and Conjugate Matching                         |

| 8.3.1 Load and Source Stability Regions                      |

| 8.3.2 Stability Factor                                       |

| 8.3.3 Conjugate Matching                                     |

| 8.4 Gain and Noise Circles                                   |

| 8.4.1 Gain Circles                                           |

| 8.4.2 Noise Circles                                          |

| 8.5 Summary of Gains and Circles                             |

| 8.5.1 Summary of Gains                                       |

| 8.5.2 Summary of Circles                                     |

| 8.6 Design Example                                           |

| 8.6.1 Design Goal                                            |

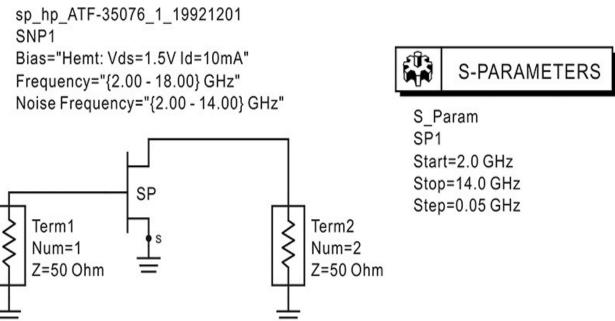

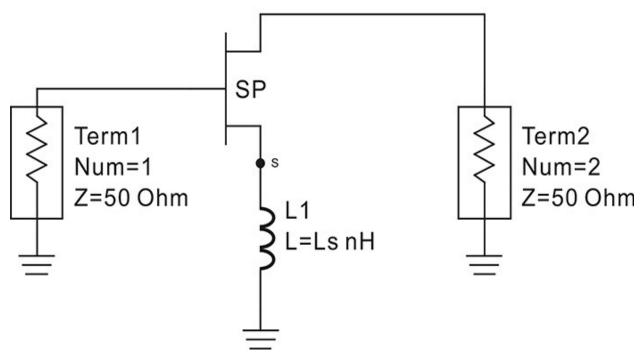

| 8.6.2 Active Device Model                                    |

| 8.6.3 Device Performance                                     |

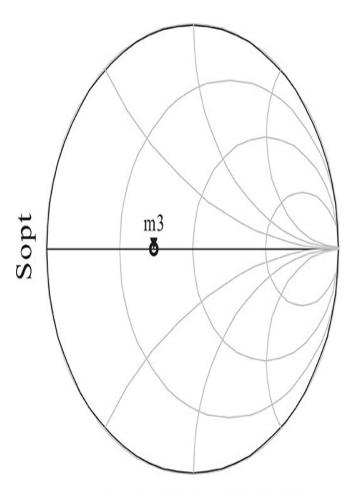

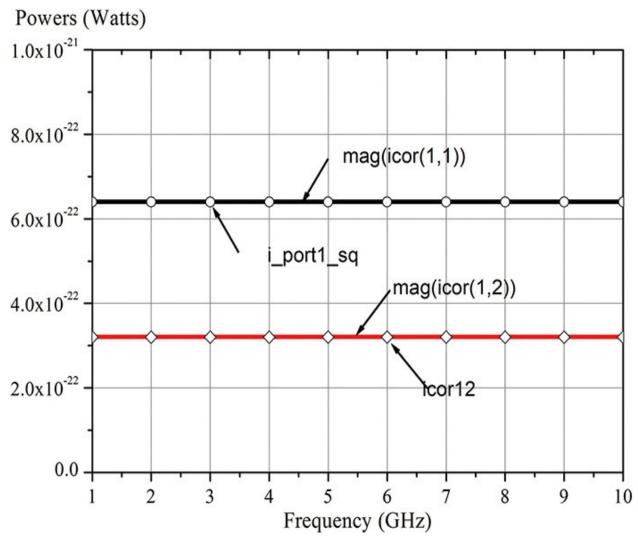

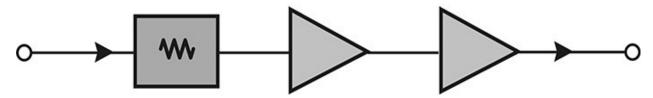

| 8.6.4 Selection of Source and Load Impedances                |

| 8.6.5 Matching Circuit Design                                |

| 8.6.6 DC Supply Circuit                                      |

| 8.6.7 Stability                                              |

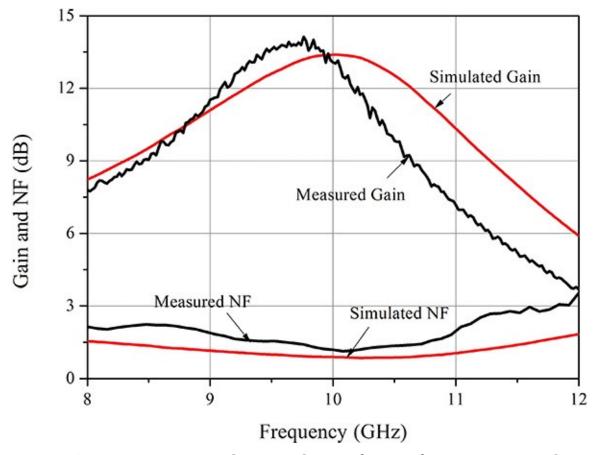

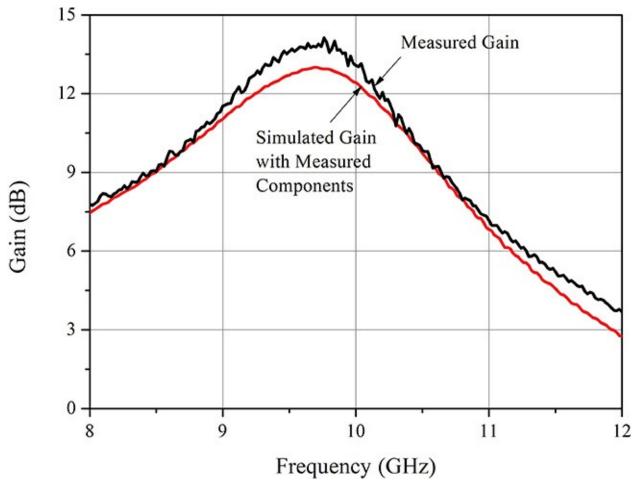

| 8.6.8 Fabrication and Measurements                           |

| 8.7 Summary                                                  |

| <b>Chapter 9 Power Amplifiers</b>                            |

| 9.1 Introduction                                      |

|-------------------------------------------------------|

| 9.2 Active Devices for Power Amplifiers               |

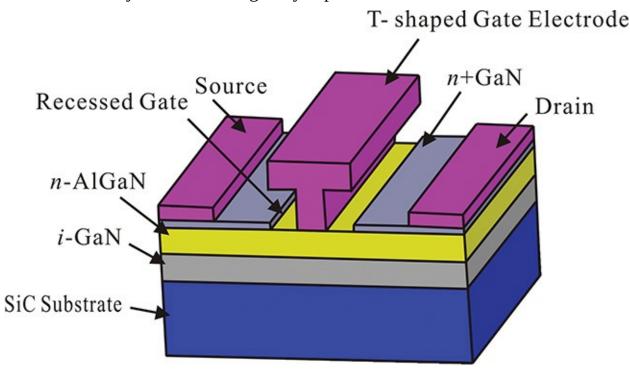

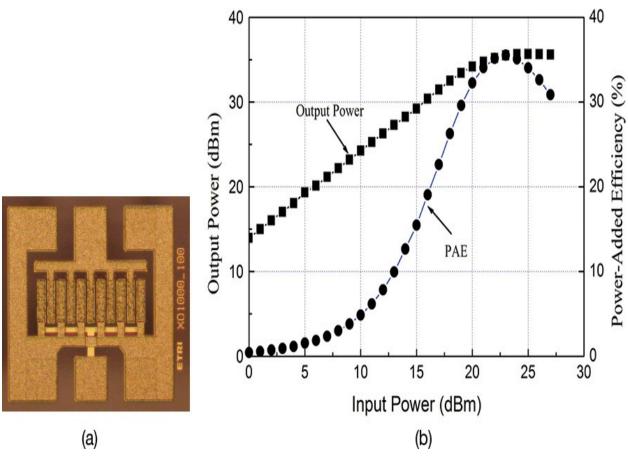

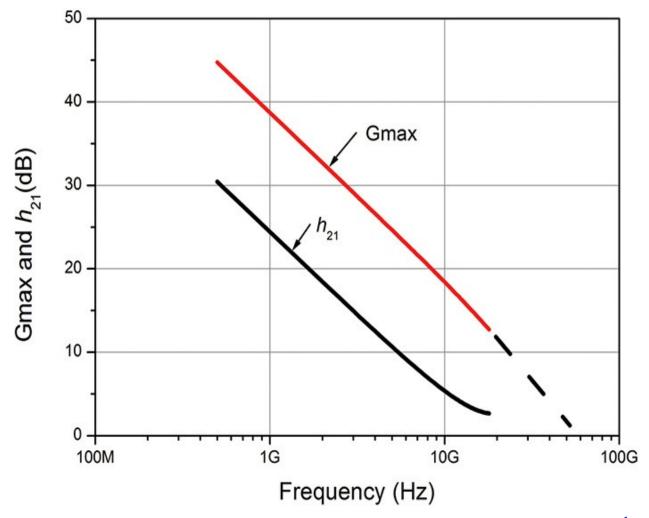

| <u>9.2.1 GaN HEMT</u>                                 |

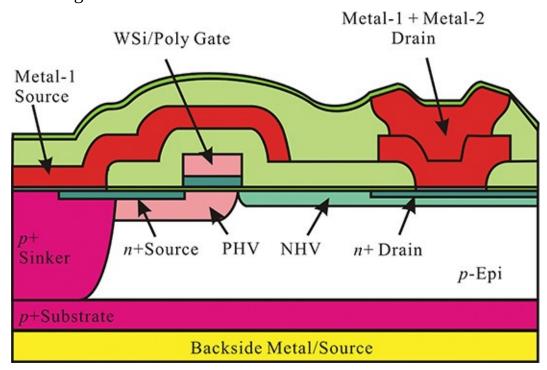

| <u>9.2.2 LDMOSFET</u>                                 |

| 9.3 Optimum Load Impedances                           |

| 9.3.1 Experimental LoadPull Method                    |

| 9.3.2 LoadPull Simulation                             |

| 9.4 Classification                                    |

| 9.4.1 Class-B and Class-C Power Amplifiers            |

| 9.4.2 Class-D Power Amplifiers                        |

| 9.4.3 Class-E Power Amplifiers                        |

| 9.4.4 Class-F Power Amplifiers                        |

| 9.5 Design Example                                    |

| 9.5.1 Optimum Input and Output Impedances             |

| 9.5.2 Input and Output Matching Circuits              |

| 9.5.3 Design of Matching Circuits Using EM Simulation |

| 9.6 Power Amplifier Linearity                         |

| 9.6.1 Baseband Signal Modulation                      |

| 9.6.2 Envelope Simulation                             |

| 9.6.3 Two-Tone and ACPR Measurements                  |

| 9.6.4 EVM Simulation                                  |

| 9.7 Composite Power Amplifiers                        |

| 9.7.1 Predistorters                                   |

| 9.7.2 Feedforward Power Amplifiers (FPA)              |

| 9.7.3 EER (Envelope Elimination and Restoration)      |

| 9.7.4 Doherty Power Amplifier                         |

| 9.8 Summary                                           |

| <b>Chapter 10 Microwave Oscillators</b>               |

| 10.1 Introduction                                     |

| 10.2 Oscillation Conditions                                                 |

|-----------------------------------------------------------------------------|

| 10.2.1 Oscillation Conditions Based on Impedance                            |

| 10.2.2 Oscillation Conditions Based on the Reflection Coefficient           |

| 10.2.3 Start-Up and Equilibrium Conditions Based on Open Loop Gain          |

| 10.3 Phase Noise                                                            |

| 10.3.1 Spectrum of an Oscillation Waveform                                  |

| 10.3.2 Relationship between Phase Noise Spectrum and Phase Jitter           |

| 10.3.3 Leeson's Phase Noise Model                                           |

| 10.3.4 Comparison of Oscillator Phase Noises                                |

| 10.4 Basic Oscillator Circuits                                              |

| 10.4.1 Basic Oscillator Circuits                                            |

| 10.4.2 Conversion to Basic Forms                                            |

| 10.4.3 Design Method                                                        |

| 10.5 Oscillator Design Examples                                             |

| 10.5.1 VCO for Mobile Communications                                        |

| 10.5.2 Microstrip Oscillator                                                |

| 10.6 Dielectric Resonators                                                  |

| 10.6.1 Operation of Dielectric Resonator (DR)                               |

| 10.6.2 Extraction of the Equivalent Circuit of a DR Coupled to a Microstrip |

| 10.7 Dielectric Resonator Oscillators (DRO)                                 |

| 10.7.1 DRO Design Based on Replacement                                      |

| 10.7.2 Dielectric Resonator Oscillator Design Using Feedback                |

| 10.7.3 Comparison between the Two DRO Design Methods                        |

| 10.8 Summary                                                                |

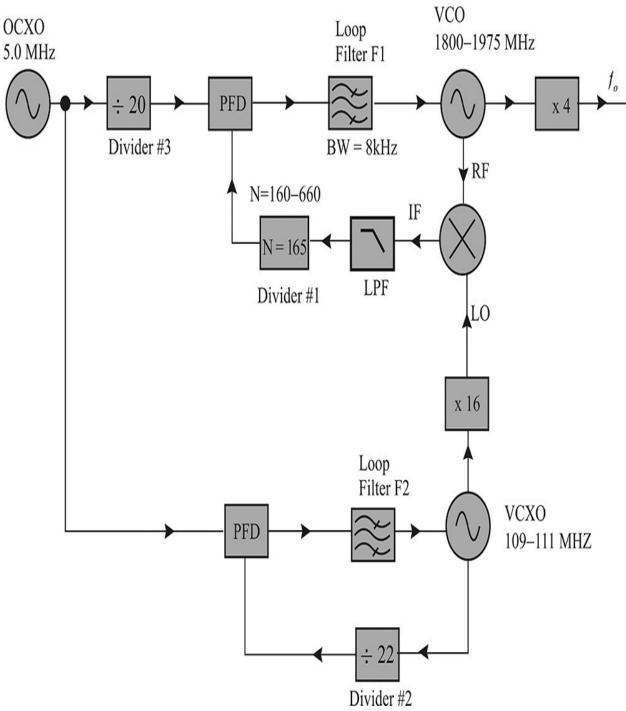

| Chapter 11 Phase-Locked Loops                                               |

| 11.1 Introduction                                   |

|-----------------------------------------------------|

| 11.2 Configuration and Operation of a PLL           |

| 11.3 PLL Components                                 |

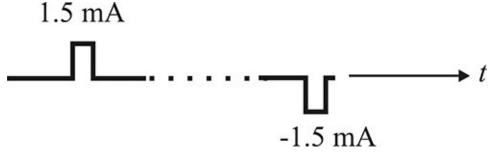

| 11.3.1 Phase Detector                               |

| 11.3.2 Frequency Divider                            |

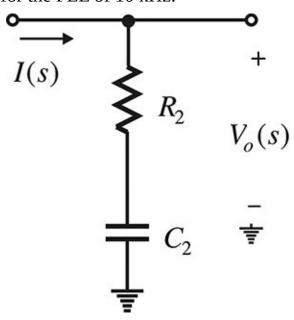

| 11.4 Loop Filters                                   |

| 11.4.1 Loop Filter                                  |

| 11.4.2 Second-Order Loop Filters                    |

| 11.4.3 Implementation of a Second-Order Loop Filter |

| 11.4.4 Measurement of a PLL                         |

| 11.4.5 Higher-Order Loop Filters                    |

| 11.5 PLL Simulation in ADS                          |

| 11.5.1 Loop Filter Synthesis                        |

| 11.5.2 Phase Noise Simulation                       |

| 11.5.3 Transient Response Simulation                |

| 11.6 Summary                                        |

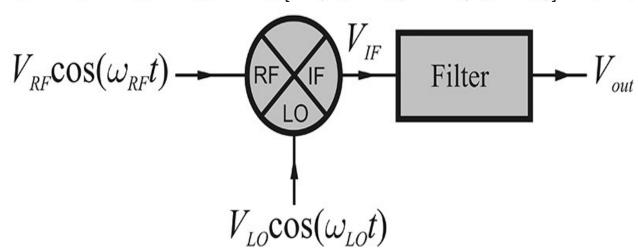

| <u>Chapter 12 Mixers</u>                            |

| 12.1 Introduction                                   |

| 12.2 Specifications                                 |

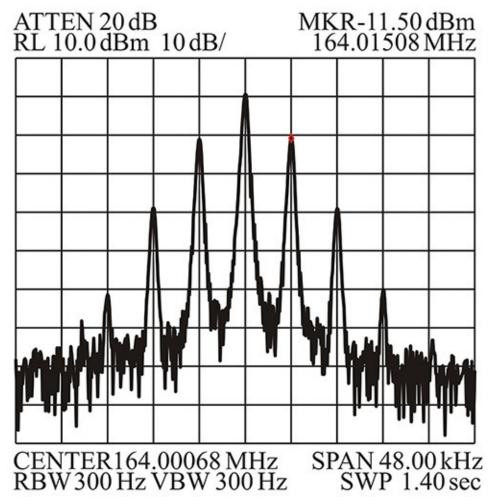

| 12.2.1 Conversion Loss and 1-dB Compression Point   |

| 12.2.2 Mixer Isolation and VSWR                     |

| 12.3 Schottky Diodes                                |

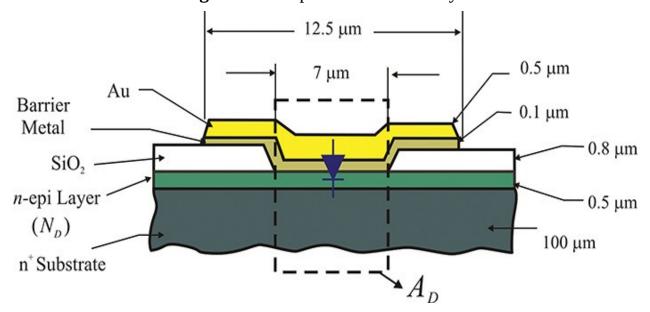

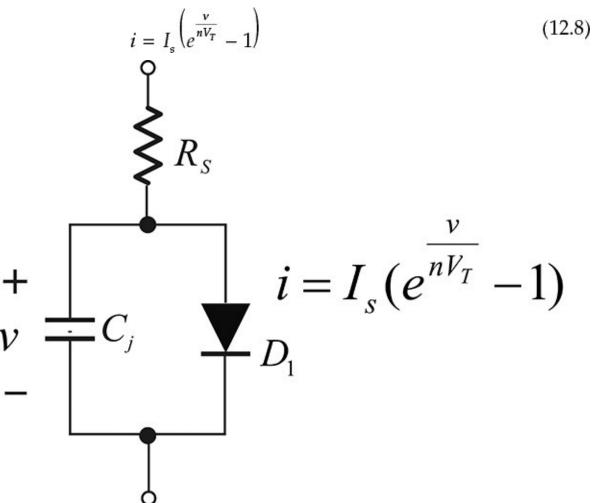

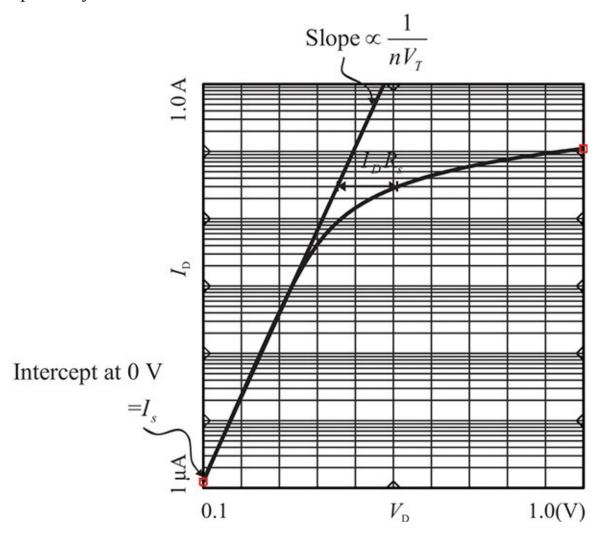

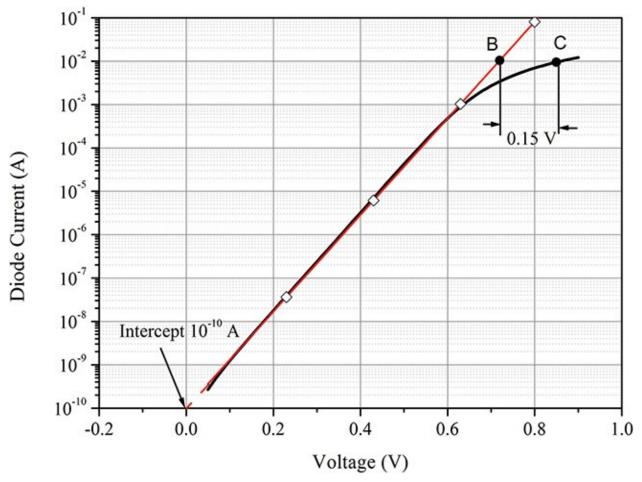

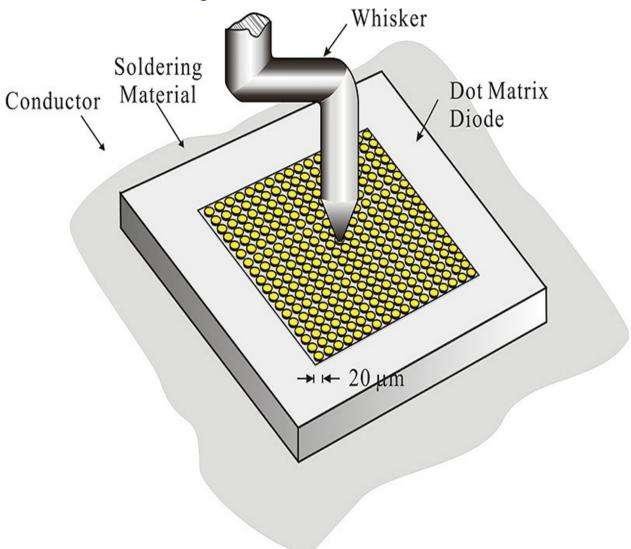

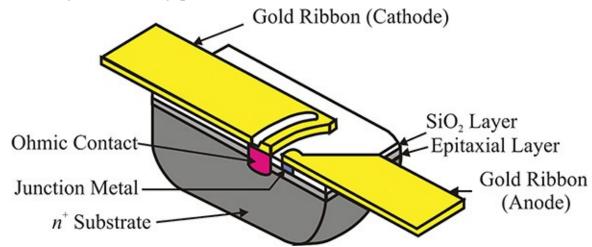

| 12.3.1 Structure of the Schottky Diode              |

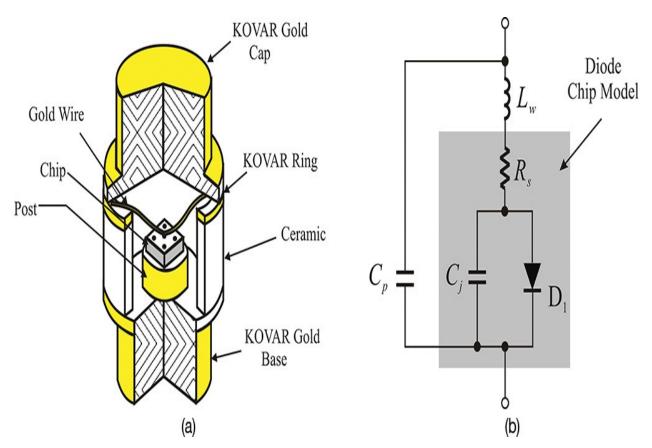

| 12.3.2 The Schottky Diode Package                   |

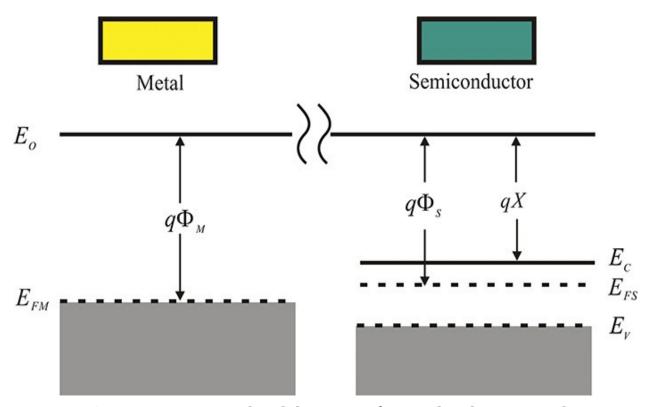

| 12.3.3 Operating Principle of the Schottky Diode    |

| 12.4 Qualitative Analysis                           |

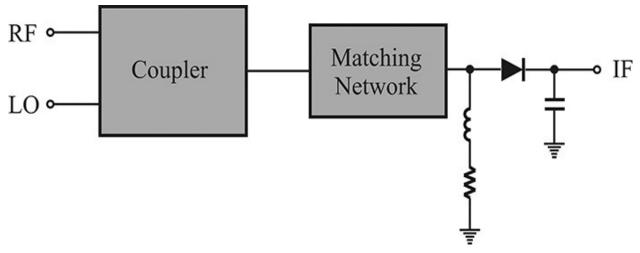

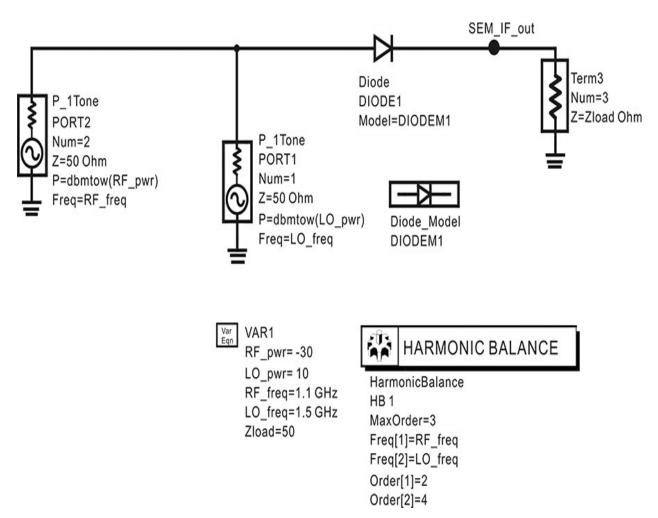

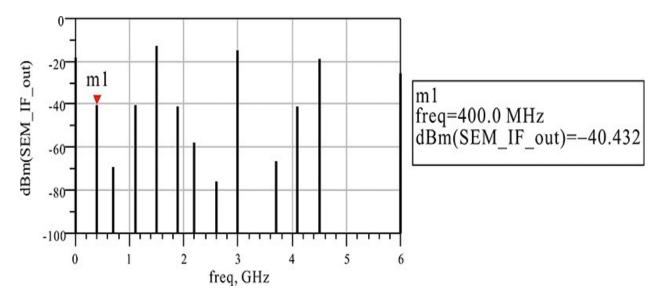

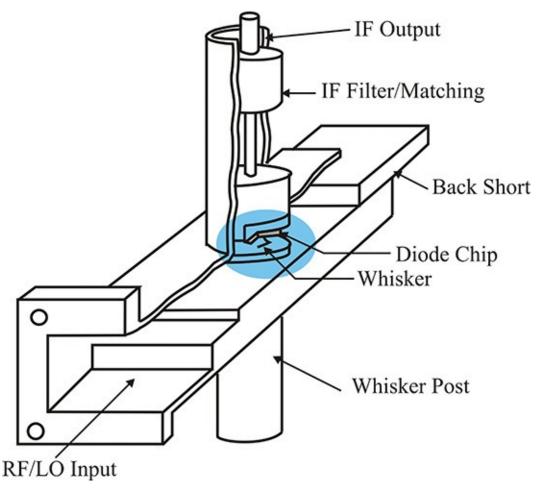

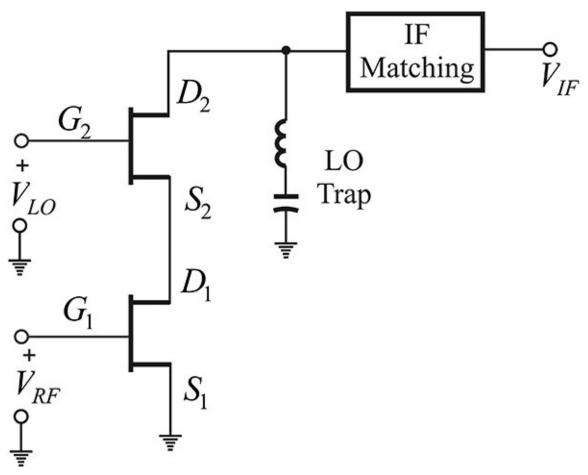

| 12.4.1 Single-Ended Mixer (SEM)                     |

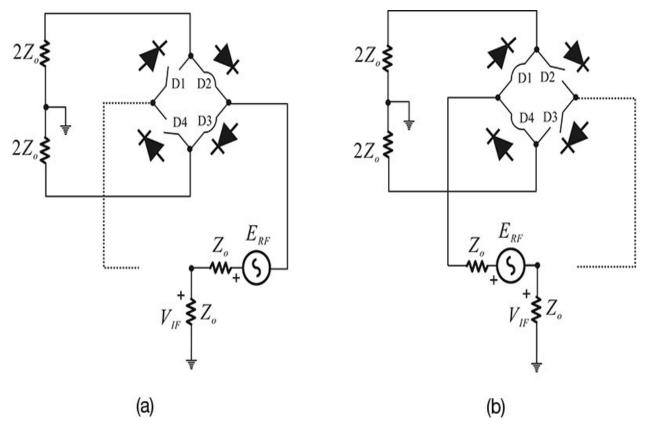

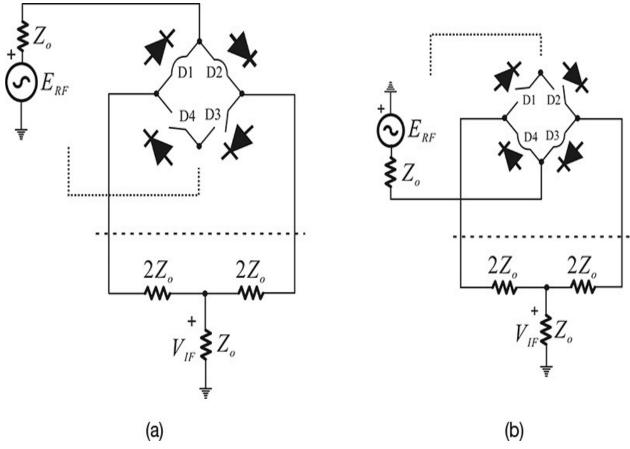

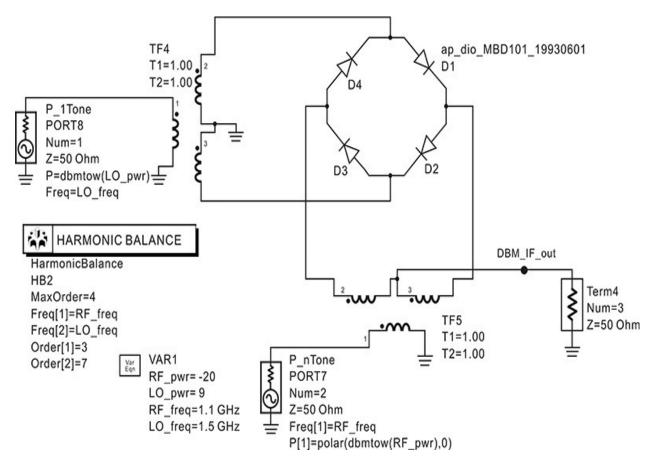

| 12.4.2 Single-Balanced Mixer                        |

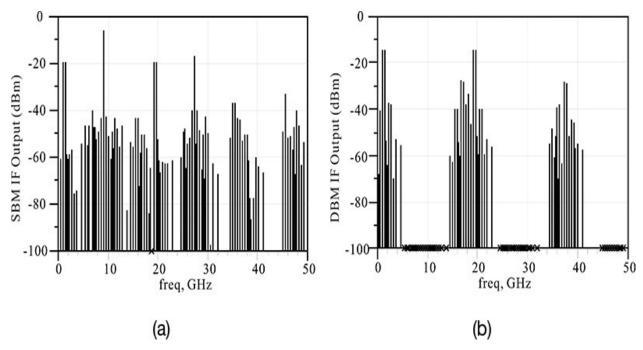

| 12.4.3 Double-Balanced Mixer (DBM)                  |

|                                                     |

## 12.4.4 Comparison of Mixers

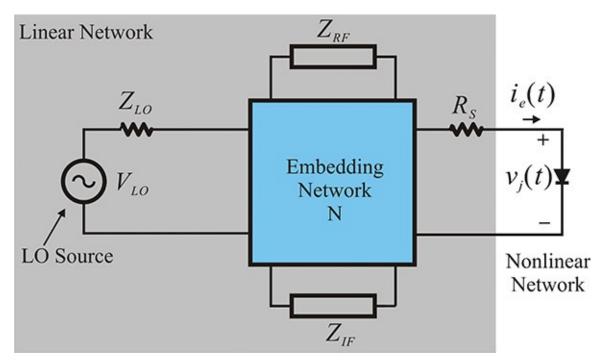

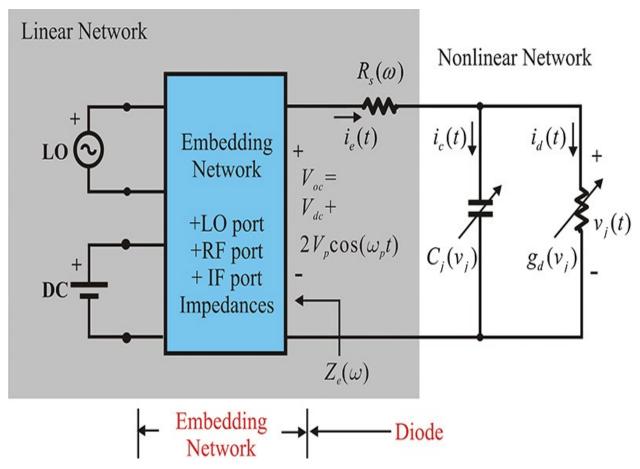

## 12.5 Quantitative Analysis of the SEM

12.5.1 LO Analysis of a Mixer

12.5.2 Small-Signal Analysis

**12.5.3 Calculation of Mixer Parameters**

#### **12.6 Summary**

## **Appendix**

- A. Units

- **B.** Cascaded Structure

- C. Half-Wave Rectifier Analysis Using Mathcad

- **D. Large-Signal Impedance and Reflection Coefficient**

- E. Mathematical Analysis of Negative Resistance

- F. Oscillation Conditions Based on Reflection Coefficients

#### **Index**

#### **Preface**

This book primarily examines **active microwave circuit design**, an important part of microwave engineering. This subject has worldwide appeal given the incredible growth in mobile and satellite communications. In the past, the use of microwaves was limited to radars and weapon systems, and to remote sensing and relay systems. However, due to the rapid expansion of mobile and satellite communication systems in recent years, systems that use radio waves or microwaves can be found in almost every sphere of our lives. Thus, it is clear there is an increased need for educational materials about active microwave circuit designs. This text is intended as a guide for graduate students who have majored in electronic engineering and its related fields. It should also be useful to engineers and professionals working in these fields who want to update their knowledge through independent study.

In writing this guide, I make the assumption that readers have majored in electronics or related fields as undergraduate students. In particular, readers are assumed to have the **prerequisite knowledge of circuit theory, electronic circuits, and electromagnetics,** which are usually covered in mandatory courses at the undergraduate level.

Numerous books have been published on the subject of active microwave circuit design. However, many of these works do not present the hands-on approach required in modern curricula, making it difficult for readers who only have the basic prerequisite knowledge mentioned above, to understand and follow such texts. For these readers, practical design skills may be hard to acquire by simply reading a text that presents only theory based primarily on mathematical explanations. On the other hand, most people working in this field have become familiar with the prevalence of design software employed in active microwave circuit designs, such as the Advanced Design System (ADS) from Agilent Technologies and Advancing the Wireless Revolution (AWR) from AWR Corporation. The design environment for active microwave circuits has changed drastically with the continuous expansion of microwave applications into our daily lives. Recently, a variety of software design tools applicable to circuit design, system design, and electromagnetic analysis of passive structures has emerged. This has significantly reduced the need for analytical methods and specific design-oriented, in-house programs for the design of circuits and systems. With these advances, the rapid exchange of

results between designers has facilitated independent study and experimentation with basic concepts using software tools and practical designs. Clearly, innovations in the field underscore the necessity for advanced education in active microwave circuit design and improvements to relevant software tools. The practical design skills for active microwave circuit designers can be effectively improved through hands-on practice with design software. More than ever, the importance of ongoing education to an engineer in this field cannot be overemphasized.

Given this perspective, it is my view that an education incorporating these features has become imperative. With more than 17 years of experience educating graduate students, I have written this guide to address the critical importance of this subject. With this book, readers will acquire **the practical skills required for active microwave circuit design** using the design software. The popular Advanced Design System (ADS) from Agilent Technologies is the design tool used in the book as it has the longest proven track record compared to other design software. However, since most features of ADS are also available in other, similar design software, I believe that selecting ADS as the design tool will not present any critical limitations to readers.

This book is primarily composed of two parts: **basic concepts for active microwave circuit designs**, and **practical design examples** such as low-noise amplifiers (LNA), power amplifiers (PA), microwave oscillators, phase-locked loops (PLL), and mixers. The designs of LNAs, PAs, oscillators, and mixers are essential in building various communication systems, radars, and other microwave transmitting and receiving systems. Additional components such as phase shifters, variable attenuators, and switches, although important, appear only in limited applications and are not used as frequently when compared to the previously mentioned set of components.

The basic concepts are concisely and clearly explained based on their physical characteristics. These concepts, essential in an introduction to an active microwave circuit design course, include passive devices, transmission-line theory, high-frequency measurement, and an introduction to active devices. For these basic concepts, this book focuses more on physical concepts and on understanding the meaning of calculated results rather than on exhaustive mathematical calculations. This is achieved by presenting critical concepts as clearly and succinctly as possible. In addition, complex calculations are avoided whenever possible and Agilent's ADS is employed to replace them. The software is used to analyze or verify the basic concepts, enabling readers to achieve a deeper and more thorough understanding of them. Pertinent, real-

world examples facilitate comprehension and independent study.

For the design of LNAs, PAs, oscillators, and mixers, readers are provided with **practical design examples** using ADS that they can subsequently use to design similar active microwave circuits. I am confident this book will provide readers with the practical skills necessary for active microwave circuit design. Finally, although the book is designed for graduate students, it can also be very helpful as source material for **independent study or as a reference book** for professionals.

The text is composed of materials that provide a two-semester course curriculum. Depending on the students, this can be reduced to a one-semester course when the foundation topics in the first part of the book are skipped or covered only briefly. For the design of LNAs, PAs, oscillators, and mixers, a project-style lecture may be useful. (After a brief explanation of the basic design components, students establish a lecture style and present their design.) A solution manual is available for instructors at Pearson's Instructor's Resource Center (IRC). I welcome and appreciate any corrections or suggestions for improvement to this content.

Register your book at <a href="informit.com/title/9780134086781">informit.com/title/9780134086781</a> to access this book's ADS examples and problems.

Kyung-Whan Yeom April 2015

## **Acknowledgments**

I am very grateful to my lab students for their efforts editing many of the figures and the contents of this textbook. Also, I would like to thank the Prentice Hall staff, and particularly Bernard Goodwin, for their support. I would especially like to express my deep appreciation to the reviewers for evaluating this text and offering valuable suggestions. Finally, I would like to thank my wife, Soon-Duk Cho, and son, Jae-Hyung Yeom, for their tolerance and support, which allowed me to write this book.

#### Reviewers

Professor Changzhi Li (Texas Tech University); Full text

Professor Jin Wang (University of South Florida); Full text

Dong-Wook Kim (Chungnam National University, Korea);

Chapter 9, 10

Professor Matthew Radmanesh (California State University, Northridge); <a href="#">Chapter 9</a>

Anonymous reviewer; Chapter 9

#### **Translation**

Abdul-Rahman Ahmed (Chungnam National University, Korea)

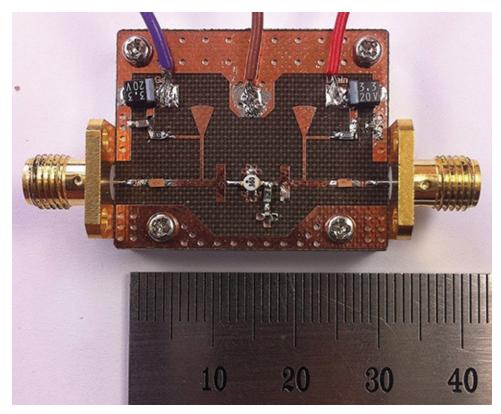

## **LNA Design Example**

Hyun-Seok Oh (Agency for Defense Department, Korea) and Dong-Hyun Lee

## **Oscillator Design Example**

Hae-Chang Jeong and Beom-Ik Son (Chungnam National University, Korea)

#### **Mixer Simulation**

Seong-Sik Yang (Samsung Thales, Korea)

## **Preparation of Manuscript and Figures**

Hyun-Mi Kim(KOMSCO, Korea)

Man-Hee Lee (LIG Nex1, Korea)

Hyun-Seok Oh (Agency for Defense Department, Korea)

Yun-Seong Heo (Hanhwa, Korea)

Hae-Chang Jeong (Chungnam National University, Korea)

Beom-Ik Son (Chungnam National University, Korea)

Seok-Jeong Lee (Chungnam National University, Korea)

#### **About the Author**

**Kyung-Whan Yeom** was born in Seoul, Korea, in 1957. He received a B.S. degree in electronics from Seoul National University in 1980 and M.S. and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1982 and 1988, respectively.

From 1985 to 1991, he worked at LG Precision as a principal engineer. He worked on the MIC team as a team leader and was later involved in the military electronics division for EW Equipment. When he was at LG Precision, he received a technical achievement award for the ABEK program from Teledyne Microelectronics.

From 1991 to 1995, he worked at LTI on power amplifier modules for analog cellular phones. He joined the Chungnam National University as assistant professor in 1995 and is currently a professor in the Department of Radio Science and Engineering, Chungnam National University, Daejeon, Korea. His research interests are in the design of hybrid and monolithic microwave circuits and microwave systems.

Professor Yeom has been a member of the Korean Institute of Electromagnetic Engineering and Science (KIEES) and the Institute of Electrical and Electronics Engineers (IEEE) since 1995. He was the editor-in-chief of KIEES from 2004 to 2006. He received the IR-52 Jang Youg-Sil Prize from the Ministry of Science and Technology (MOST) of Korea for his work on cell phone power amplifiers in 1994. He received an academic award from KIEES for the design and fabrication of a novel 60 GHz GaAs pHEMT resistive double balanced star MMIC mixer in 2004. He also received the best paper award from the Korean Federation of Science and Technology Societies (KOFST) for his work, "A Novel Design Method of Direct Coupled Bandpass Filter Based on EM Simulation of Individual Resonator."

# **Chapter 1. Microwave Integrated Circuits**

## **Chapter Outline**

- 1.1 Classification of Microwave Integrated Circuits

- 1.2 Microwave Circuits in a Communication System

- 1.3 Summary

## 1.1 Classification of Microwave Integrated Circuits

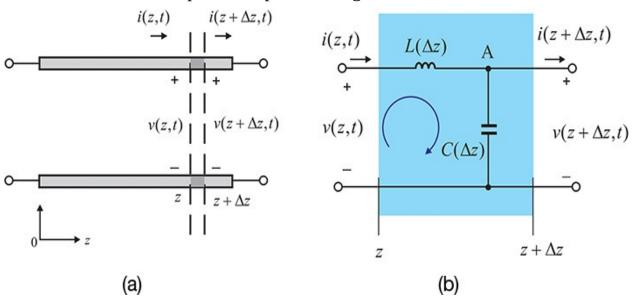

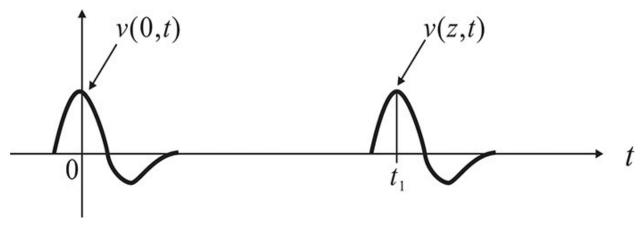

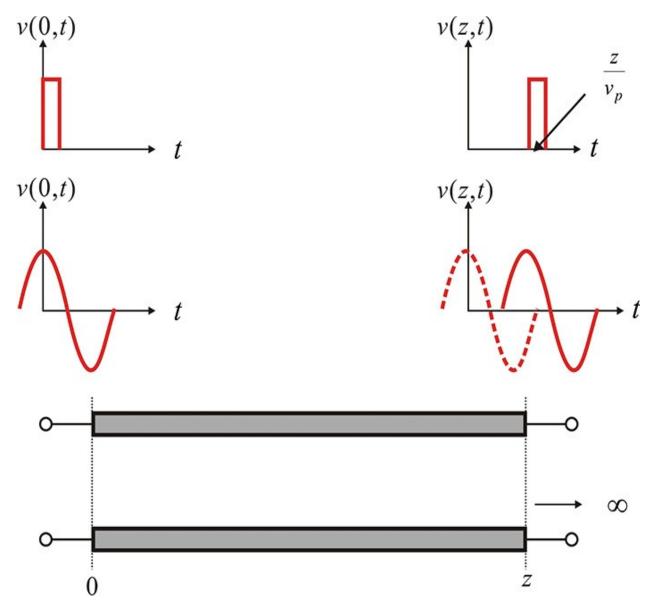

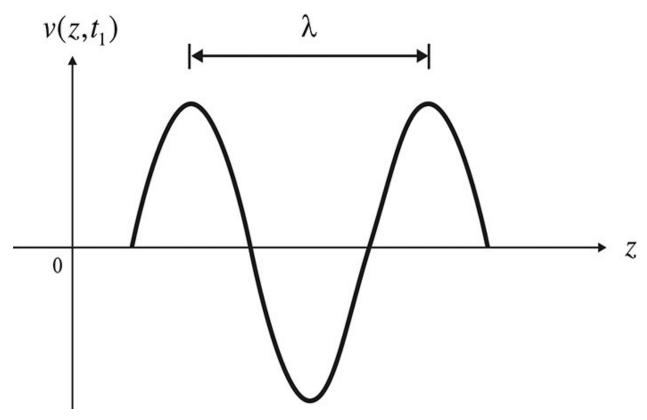

An active microwave circuit can be defined as a circuit in which active and passive microwave devices such as resistors, capacitors, and inductors are interconnected by transmission lines. At low frequencies, the transmission lines are a simple connection; however, at microwave frequencies they are no longer just simple connections and their operation becomes a complicated distributed circuit element. As a result, a microwave integrated circuit's classification is based on the fabrication method of the transmission lines used for interconnection.

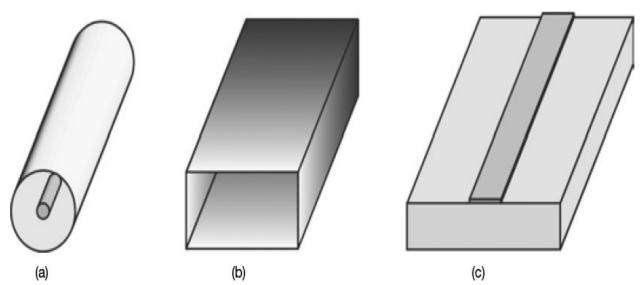

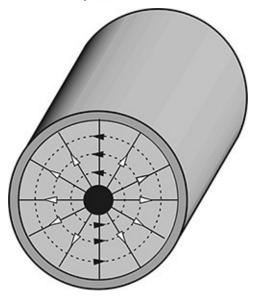

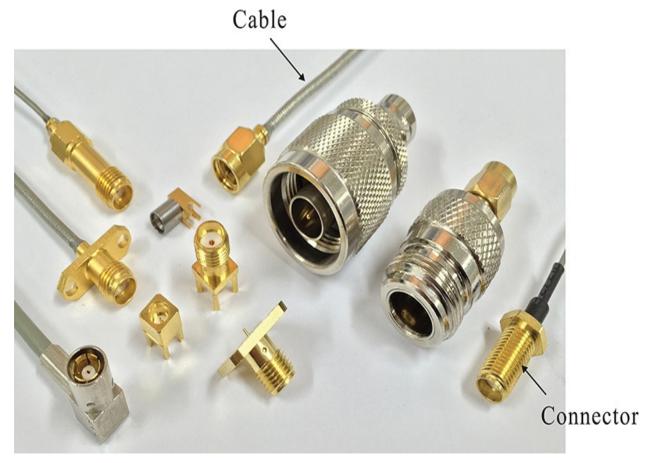

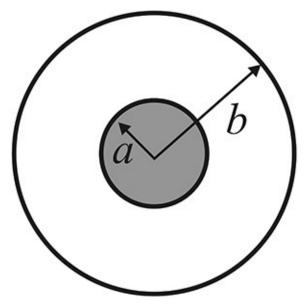

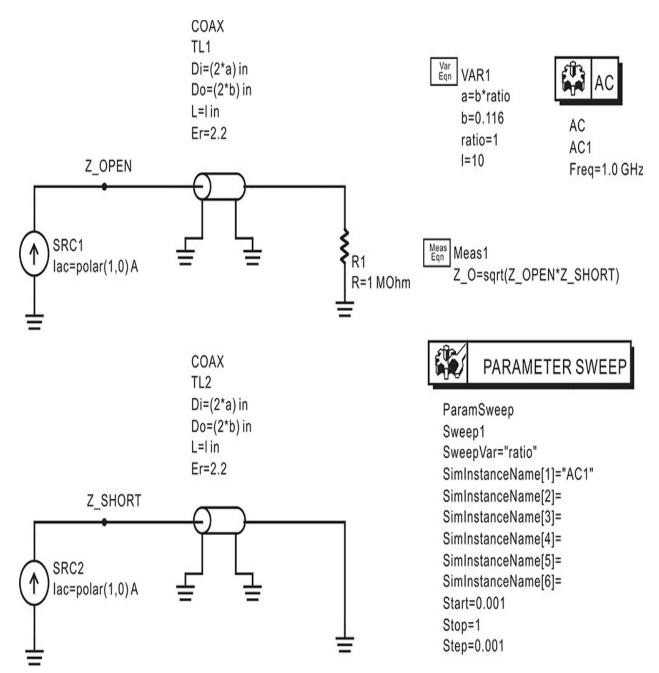

There are various types of transmission lines in microwave integrated circuits; some common examples are waveguides, coaxial, and microstrip lines. Figure 1.1 shows the transmission lines used in microwave circuits. Although there are special cases of microwave integrated circuits that are composed of coaxial lines and waveguides, in most cases the microwave integrated circuits are formed using planar transmission lines. Therefore, the content of this book is restricted to microwave integrated circuits formed using planar transmission lines, examples of which are microstrip, slot line, and coplanar waveguide (CPW), as shown in Figure 1.2. These planar transmission lines are frequently used in the large-scale production of microwave circuits and generally form the basic transmission lines for microwave circuits.

**Figure 1.1** Some common transmission lines used in microwave circuits: (a) coaxial line, (b) rectangular waveguide, and (c) microstrip line

**Figure 1.2** Some common planar transmission lines used in microwave circuits: (a) microstrip, (b) slot line, and (c) CPW (coplanar waveguide). They are explained in <u>Chapter 3</u>.

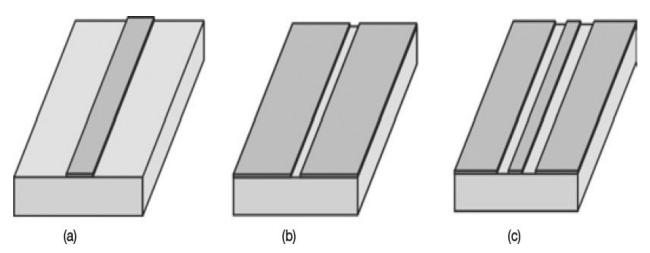

The implementation of planar transmission lines on substrates can be classified into two basic groups: *monolithic* and *hybrid integrated circuits*. In monolithic integration, the active and passive devices as well as the planar transmission lines are grown *in situ* on one planar substrate that is usually made from a semiconductor material called a *wafer*.

Figure 1.3 shows an example of monolithic integration. Figure 1.3(a) is a photograph of the top side of a wafer and Figure 1.3(b) shows a single monolithic microwave integrated circuit; the identical circuits are repeatedly produced on the wafer in Figure 1.3(a). The monolithic microwave integrated circuit in Figure 1.3(b) is found to contain active and passive devices, and planar transmission lines. The monolithic integration provides a compact-sized circuit and eliminates a significant amount of assembly when building a component or a system. Especially because size is of critical importance in most recent RF systems, monolithic integration is frequently employed to provide a compact component. An advantage of monolithic integration is that it is well suited for large-scale production, which results in lower costs. A disadvantage is that monolithic integration takes a long time to develop and fabricate, and small-scale production results in highly prohibitive costs.

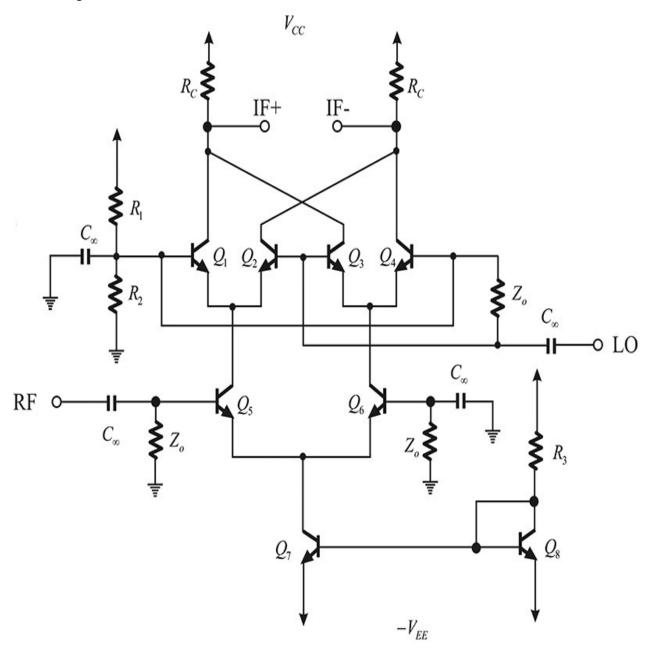

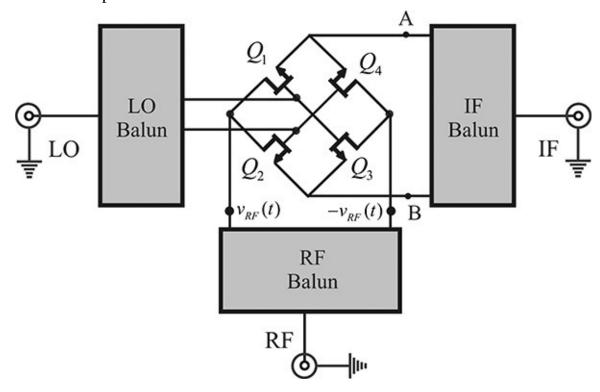

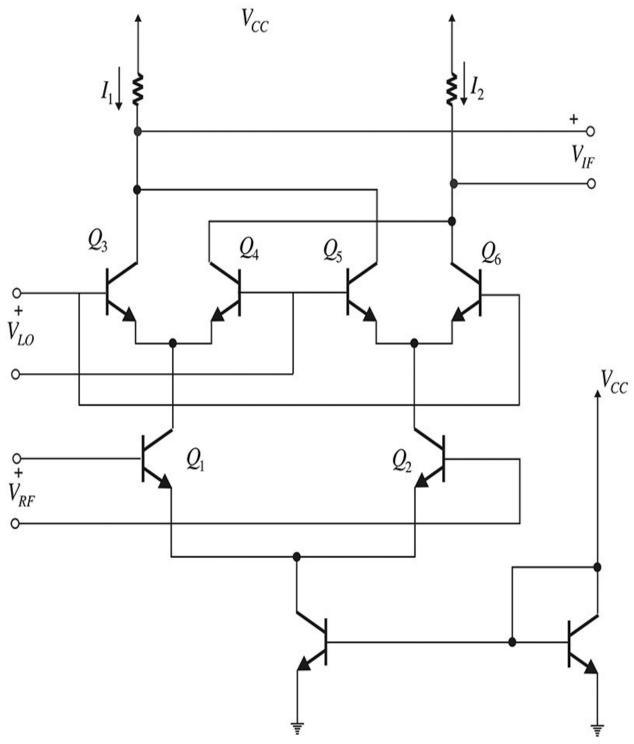

**Figure 1.3** Monolithic integration: (a) a wafer and (b) a monolithic microwave integrated circuit on the wafer (28 GHz GaAs pHEMT Gilbert cell up-converting mixer; refer to <a href="Chapter 12">Chapter 12</a>).

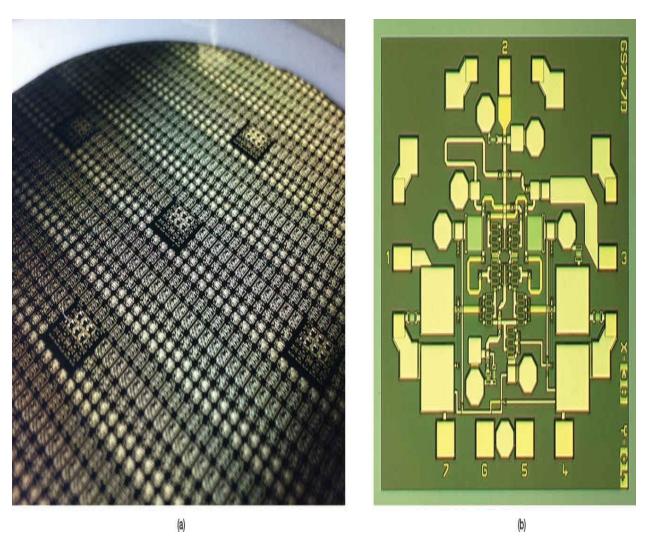

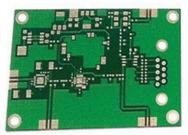

Hybrid integration is a fabrication method in which the transmission lines are implemented by conductor patterns on a selected substrate with either *printing* or *etching*, and active and passive devices are assembled on the patterned substrate by either soldering or wire bonding. When implementing transmission lines by conductor patterns on a substrate, careful consideration must be given to the substrate material and the conductor material for the transmission lines because these materials can have significant effects on the characteristics of transmission lines. Hybrid integration is thus classified into three types based on the method by which the lines are formed on the substrate: a *printed circuit board* (PCB), a *thick-film* substrate, and a *thin-film* substrate.

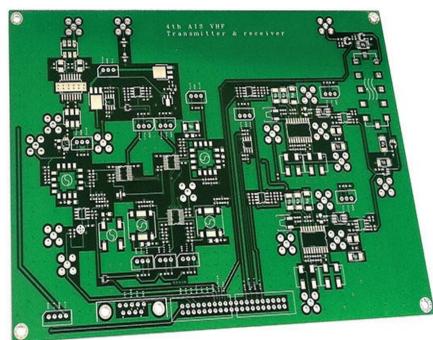

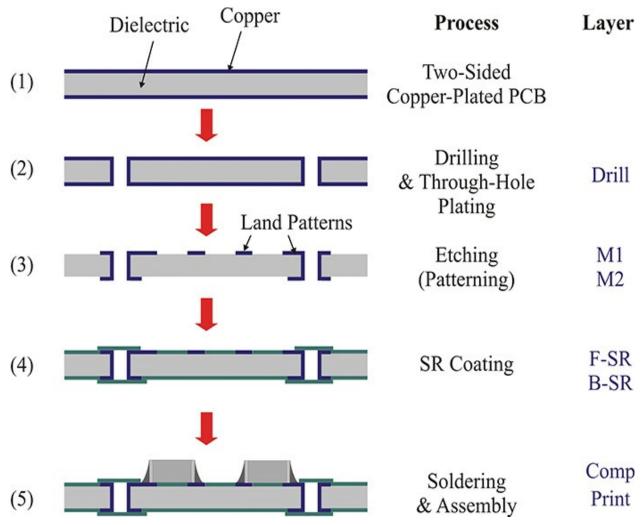

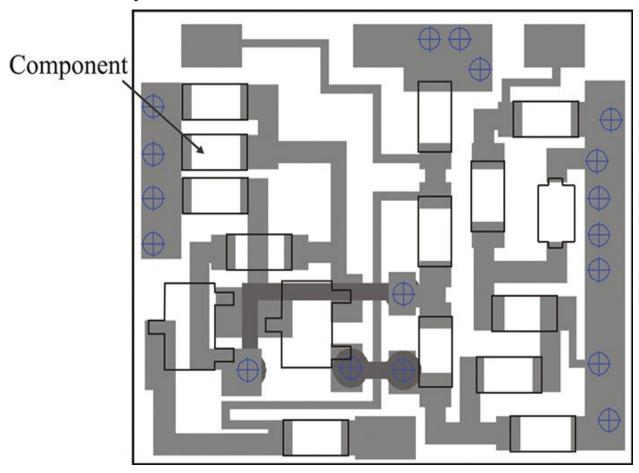

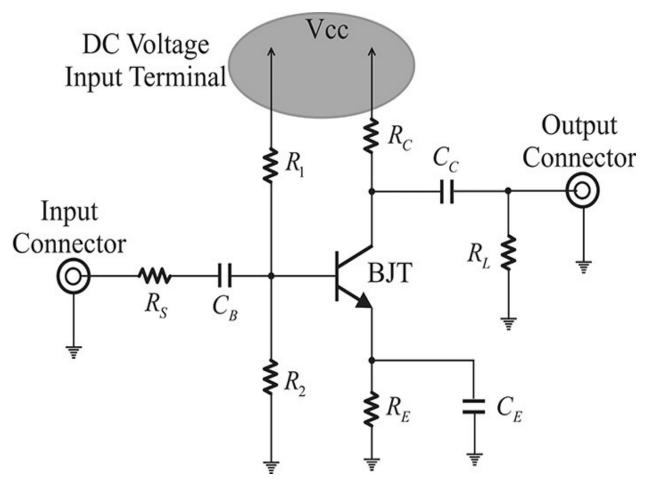

Figure 1.4 shows an example of how connection lines are formed on a PCB

substrate. Both sides of the dielectric material are attached with copper cladding that is then etched to obtain the desired conductor patterns. For PCB substrate materials, *epoxy fiberglass* (FR4), *teflon*, and *duroid* are widely used. FR4 substrate (a kind of epoxy fiberglass) can be used from lower frequencies to approximately 4 GHz, while teflon or duroid can be used up to the millimeter wave frequencies, depending on their formation. Generally, all these materials lend themselves to soldering while wire bonding for an integrated circuit assembly is typically not widely used. Furthermore, compared with other methods that will be explained later, a PCB can result in lower costs; its fabrication is easy and requires less time to produce. In addition, production on a small scale is possible without the use of expensive assembly machines; it is easy to fix and could also be used in large-scale production, and is thus widely used.

**Figure 1.4** A photograph of epoxy fiberglass PCBs. The PCBs on the left are for the X-band and 2 GHz frequency synthesizers using the phase locked loop. The PCB on the right is for the VHF automatic identification system, which has a similar block diagram shown in Figure 1.7. The power amplifier is implemented in a separate block.

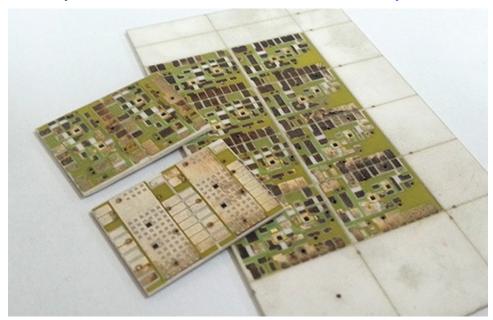

Thick-film substrates are produced by screen-printing techniques in which conductor patterns are formed by pushing conductive paste on a ceramic substrate through a patterned screen and then firing printed conductor patterns. The substrate is called thick film because the patterns formed by such techniques

are generally much thicker than those formed using thin-film techniques. As a benefit of using screen-printing techniques, multiple screen printings are possible. Dielectric or resistor patterns can also be formed by similar screenprinting techniques using dielectric or resistor pastes. Using an appropriate order of multiple screen printings, it is also possible to form capacitors and resistors on the ceramic substrate. Since the ceramic substrate is more tolerant of heat, it is easy to assemble active devices in the form of chips. On the other hand, considering the lines and patterns formed by this process, the pattern accuracy of thick film is somewhat inferior compared to that of thin film. The costs and development time, on a case-by-case basis, are somewhere between those of the PCB and thin-film processes. Recently, however, the integration based on thickfilm technology has become rare because its cost and pattern accuracy are between the PCB and thin-film technology, while thick film is widely used to build multifunction components. A typical example is the package based on LTCC (low-temperature co-fired ceramics) technology. Multilayer ceramics and structuring are possible in LTCC technologies. Figure 1.5 shows a photograph of thick-film patterned substrates fabricated using the thick-film process.

1. Refer to Barry LTCC, LTCC Surface Mount T/R Module, at www.barryind.com.

**Figure 1.5** A photograph of substrates fabricated by the thick-film process. Identical circuits can be arrayed for efficient production. This circuit is for the mobile communication VCO presented in <a href="#">Chapter 10</a>.

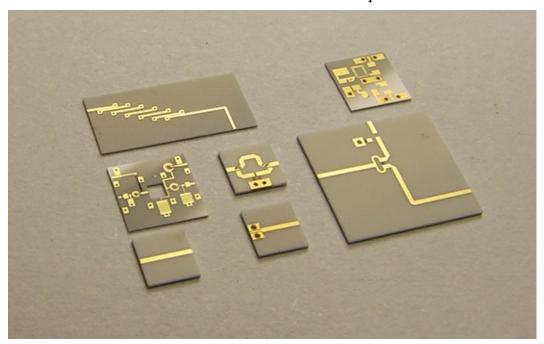

The thin-film technique is very widely used in the fabrication of microwave circuits for military and microwave communication systems. In the case of the thin-film process, a similar ceramic substrate material used in thick film is

employed, but compared to the thick-film substrate, a fine surface-finish substrate is used. The most widely used substrate is 99% alumina (Al<sub>2</sub>O<sub>3</sub>). Other substrates such as fused silica, quartz, and so on are possible for conductorpattern generation based on thin-film technologies. The pattern formation on the substrate is created with a photolithographic process that can produce fine tracks of conductor patterns similar to those in a semiconductor process. Since the thinfilm substrate is also alumina as in the case of a thick-film substrate, the assembly of semiconductor chips using wire bonding is possible. Thin film compared with PCB and thick film is more expensive, and due to the requirement of fine tracks, a mask fabrication is necessary and the process generally takes longer. Passive components such as resistors and air-bridge capacitors can be implemented using this process. In addition, integrated circuits produced by the thin-film process require special wire bonders and microwelding equipment for assembly. Compared to the monolithic integration process, the thin-film process tends to be cheaper in terms of cost, but compared to MMIC, the assembled circuit using the thin-film patterned substrate is difficult to characterize precisely because of unknown or poorly described parasitic circuit elements associated with the assembly methods such as wire bonding and die attach. Before the emergence of MMICs (monolithic microwave integrated circuits), thin-film technology was the conventional method for building microwave-integrated circuits (MICs). Figure 1.6 is a photograph of thin-film circuits fabricated with the thin-film technique.

**Figure 1.6** A photograph of substrates produced by the thin-film process.

From top left to bottom right, they are filter, phase shifter, power amplifier (presented in Chapter 9), path-switching circuit by assembly, power divider, and  $50 \Omega$  lines.

The choice of integration method depends on the application and situation, taking into account several factors mentioned previously, such as the operating frequency of the integrated circuit, the types of semiconductor components (chip or packaged), the forms of the passive components, large-scale fabrication costs, and method of assembly. These factors should all be considered when selecting the optimum method of integration. For a description of microwave-patterned substrate fabrication, assembly with wire bonding and soldering, and packaging, see reference 1 at the end of this chapter. The book provides general information about microwave-circuit fabrications. Table 1.1 provides a comparison of the hybrid integrations described previously.

| Technology | Cost   | Fabrication<br>Time | Pattern<br>Accuracy | Assembly                   |

|------------|--------|---------------------|---------------------|----------------------------|

| PCB        | Low    | Short               | Low                 | Soldering                  |

| Thick film | Middle | Middle              | Low                 | Soldering and wire bonding |

| Thin film  | High   | Long                | Fine                | Soldering and wire bonding |

**Table 1.1 Comparison of hybrid integration**

Now we will consider the application of the planar transmission lines such as microstrip, slot, and CPW to the monolithic and hybrid integration technologies. Microstrip lines are the most widely used transmission lines for both monolithic and hybrid integration technologies. In microstrip lines, the top conductor pattern is usually connected to the ground by a through hole or a via hole. Thus, the back-side process for the through-hole or via-hole fabrication is essential to building a circuit based on microstrip lines. This back-side process is inconvenient especially in the monolithic integration. In hybrid integration, the holes can be fabricated through simple mechanical drilling for a PCB case and through laser or ultrasonic drilling for thick-and thin-film cases. Then, plating the fabricated holes completes the fabrication of a through or via hole. However, to fabricate via holes in monolithic integration, a wafer that typically has a normal thickness of about 600  $\mu m$  should be polished down to about 100  $\mu m$ thickness. Current technology does not support via-hole fabrication beyond 100 μm. In Figure 1.2, we can see that the CPW and slot lines do not need the backside metallic ground and they eliminate the need for any additional back-side metallization process. The CPW is very helpful in monolithic integration and is widely used to build MMICs without vias. However, the discontinuities of CPWs are not well understood compared to those of microstrip lines and the integration based on a CPW is not as popular as that based on a microstrip. The various discontinuities of microstrip and slot lines, CPWs, and planar transmission lines are covered in reference 2 at the end of this chapter.

## 1.2 Microwave Circuits in a Communication System

Microwave integrated circuit classification has been discussed previously. The microwave integrated circuit was classified according to the method of implementing the planar transmission lines for the purpose of connecting active and passive devices. The functions of microwave integrated circuits vary greatly and we will now consider several important microwave integrated circuits, the designs of which will be discussed in later chapters. Some examples of these circuits are low-noise amplifiers (LNA), power amplifiers (PA), oscillators, mixers, directional couplers, switches, attenuators, and filters, among a host of other microwave-integrated circuits. Among these, directional couplers, switches, attenuators, filters, and so on, are basically passive microwave circuits, although they are very widely used. Thus, they are not covered in this book because they are considered to be outside its scope. In addition, although components such as switches, variable attenuators, phase shifters, and other control circuits are important and are composed of semiconductor devices, they are generally not regarded as the basic building blocks of a wireless communication system. Therefore, this book will only cover low-noise amplifiers, power amplifiers, oscillators, and mixers, which are the most widely used circuits in the construction of wireless communication systems. The basic design theory of these circuits as well as the devices related to them will be explained in this book.

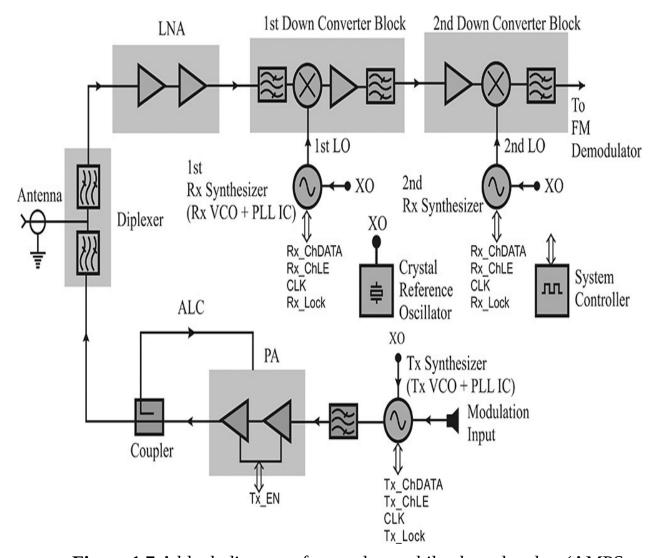

As an example of a wireless communication system, Figure 1.7 shows a block diagram of an analog cellular phone handset (Rx frequency is 869–894 MHz and Tx frequency is 824–849 MHz). A general transceiver used for the transmission and reception of analog signals (usually voice) has a similar block diagram that is shown in Figure 1.7. A weak RF signal with a typical power level of about – 100 dBm (0.1 nW) received from an antenna first goes through a filter called a diplexer and the signal is received only in the receiver frequency band. The filtered signal is too weak for direct demodulation or signal processing, and a low-noise amplifier (LNA) with a gain of 20–30 dB is required to amplify the received signal. Too much gain may cause distortion and an LNA with a gain of 20–30 dB is usually employed. Chapter 8 provides a detailed explanation of the design of an LNA.

<sup>2.</sup> Refer to AMPS (Advanced Mobile Phone System) standard.

**Figure 1.7** A block diagram of an analog mobile phone handset (AMPS standard). Tx\_EN stands for Tx enable and ALC stands for automatic level control. Tx\_ and Rx\_data are required to set the programmable frequency dividers in Tx and Rx synthesizers. LE stands for Load Enable. When LE is high, the digital channel data are loaded to the corresponding programmable frequency divider in PLL IC. Synthesizers are explained in <a href="Chapter 11">Chapter 11</a>. Lock signal indicates that the synthesizer using PLL is in a locked state.

Next, because the received signal frequency is so high, the first mixer shown in Figure 1.7 translates the carrier frequency to a lower frequency band called first IF (intermediate frequency). A double-conversion superheterodyne receiver is more widely used than a single-conversion super heterodyne receiver in a communication system. The filter in front of the first mixer again suppresses both the image frequency signal and other signals at the outside of the receiving

frequency band. Since multiple users in service are using the same frequency band, multiples of other user signals generally coexist with the signal in the first IF. Intermodulations among the multiple signals are one of the crucial issues in mixer design. Chapter 12 describes the typical topologies of various mixers for suppressing such spurious signals. In order to filter out possible spurious signals that appear at the first mixer output, the signal is passed through a narrow bandpass filter that has a bandwidth of about the signal bandwidth. The first IF filter removes many unwanted spurious signals although it may not be completely sufficient. The first IF output is converted again through the second mixing. Now the center frequency of the second IF is low enough, the highly selective filter is available, and the spurious signals can be sufficiently suppressed through the second IF filter. In addition, the signal frequency is low enough and can be demodulated for the recovery of the original signal. The demodulator is an FM demodulator and is almost the same as the FM demodulator that is commercially popular.

Note that the mixer requires the input signal from a local oscillator (LO) for the translation of the signal frequency to the IF. The two LO signals are supplied from the two Rx-synthesizers and each Rx-synthesizer consists of a voltagecontrolled oscillator (VCO) and a commercial PLL (phase-locked loop) IC (integrated circuit). Since the frequency of most VCOs is not stable enough to be used in such communication systems, the frequency of a VCO must be stabilized using a stable crystal oscillator (XO in Figure 1.7) with a typical temperature stability of 2 ppm (parts per million) and a phase-locked loop (PLL). Furthermore, the LO frequency should be moved up and down according to the base station commands. Such frequency synthesis and stabilization can be achieved by a phase-locked loop (PLL). To build a frequency synthesizer using PLL, the VCO frequency as well as the crystal oscillator frequency must be divided by appropriate programmable frequency dividers in the PLL IC. The signals CLK, Rx\_ChDATA, Rx\_ChLE, and Rx\_Lock, shown in Figure 1.7, are the digital signals between the PLL IC and the system controller. The clock signal CLK is used for the timing reference signal that is generated by the system controller using the crystal oscillator. Rx\_ChDATA sent from the controller represents the digital data to set the programmable frequency dividers. The signal Rx\_ChLE selects the corresponding programmable divider for Rx\_ChDATA to be loaded among several frequency dividers in the PLL IC. When phase lock is achieved, the PLL IC sends the signal Rx Lock to the system controller to inform the phase lock completion. The two Rx synthesizers are necessary for the double-conversion superheterodyne receiver. The

commercial PLL IC generally includes the necessary components to achieve the phase lock for two VCOs in a single PLL IC. Thus, the LO signal for the second conversion is similarly synthesized using a single PLL IC. The design of the Tx and Rx VCOs in <u>Figure 1.7</u> as well as the other microwave VCOs are described in <u>Chapter 10</u>, while the PLL's operation is explained in <u>Chapter 11</u>.

In the transmission operation, the modulation input signal (usually voice) goes to the modulation input of a Tx synthesizer. The Tx synthesizer is similarly composed of a VCO and a PLL IC. Through the PLL IC, the desired carrier center frequency is similarly synthesized as in the Rx synthesizer. The digital signals CLK, Tx\_ChDATA, Tx\_ChLE, and Tx\_Lock are similarly interpreted as in the Rx synthesizer. The modulation signal has a generally higher frequency than the PLL loop bandwidth and thus can modulate a VCO without the effects of a PLL. Therefore, the frequency-modulated (FM) signal appears at the Tx synthesizer output with the synthesized carrier frequency. The modulated signal then passes through the bandpass filter that removes unnecessary or spurious signals. The average output power level of the modulated signal is generally low; thus, in order to obtain the desired RF power output level, the signal must be amplified by a power amplifier (PA) whose typical maximum output power level is about 1W. The function ALC (Automatic Level Control) is generally built in to control the transmitting power level. When a user is close to the base station, the transmitting power level is set to low; otherwise, it is set to high for a better quality of communication. The PA output signal is then passed through a diplexer without affecting the receiver and radiated via the antenna. A power amplifier is important in this type of communication system because it consumes most of the DC power supplied from a battery. Furthermore, because a power amplifier operates in large-signal conditions, significant distortion arises. In Chapter 9, we will discuss the design and linearity evaluation of a power amplifier.

Given the preceding discussion, the key circuits in building a communication system are a low-noise amplifier, a power amplifier, oscillators, and mixers. With that in mind, this book will discuss in detail the design and evaluation method of these circuits.

## 1.3 Summary

- Microwave integrated circuits can be classified according to the fabrication method of the patterned substrate and in terms of monolithic and hybrid integration. Hybrid integration can be further classified into integrations based on PCB, thick film, and thin film. In the selection of integration, one type cannot be said to be superior to the other; the choice is made depending on the application and given situation, and by taking into consideration several factors such as cost, time, pattern accuracy, and assembly.

- Among active microwave circuits, the most commonly used building blocks for wireless communication systems or other systems, such as repeaters, transponders, and radars, are amplifiers, oscillators, and mixers.

#### References

- 1. T. S. Lavergetta, *Microwave Materials and Fabrication Techniques*, Dedham, MA: Artech House, Inc., 1984.

- 2. K. C. Gupta, *Microstrip Lines and Slot Lines*, 2nd ed. Dedham, MA: Artech House, Inc., 1996.

#### **Problems**

- **1.1** A waveguide generally has lower line loss than a microstrip. An SIW (substrate integrated waveguide) can be considered as the planar version of a waveguide. How is an SIW configured using a substrate?

- **1.2** Find the TR (transmission and receiving) module example built using a LTCC on the Web site <a href="https://www.barrvind.com">www.barrvind.com</a>.

- **1.3** How is the ALC in Figure 1.7 constructed?

- **1.4** Refer to the FM demodulator IC SA605, which is used to demodulate an FM signal. Explain how the FM signal is demodulated using its block diagram.

- **1.5** Refer to the Web site of vendors of PLL IC such as Analog Devices Inc. or other companies. Explain the synthesizer data bus shown in <u>Figure 1.7</u>.

- **1.6** How can the PLL be modulated? Explain how to set the PLL loop

bandwidth by taking the bandwidth of a bandlimited modulation signal into consideration.

# **Chapter 2. Passive Devices**

## **Chapter Outline**

- 2.1 Impedances

- **2.2 Classification**

- 2.3 Equivalent Circuits

- 2.4 Impedance Measurements

- 2.5 Summary

# 2.1 Impedances

Passive devices include resistors, capacitors, and inductors. When these devices are used in a circuit, their most fundamental property is their impedance. The impedance Z of a resistor, capacitor, and inductor are expressed, respectively, below in Equations (2.1)–(2.3).

$$Z_R = R (2.1)$$

$$Z_c = \frac{1}{j\omega C} \tag{2.2}$$

$$Z_{t} = j\omega L \tag{2.3}$$

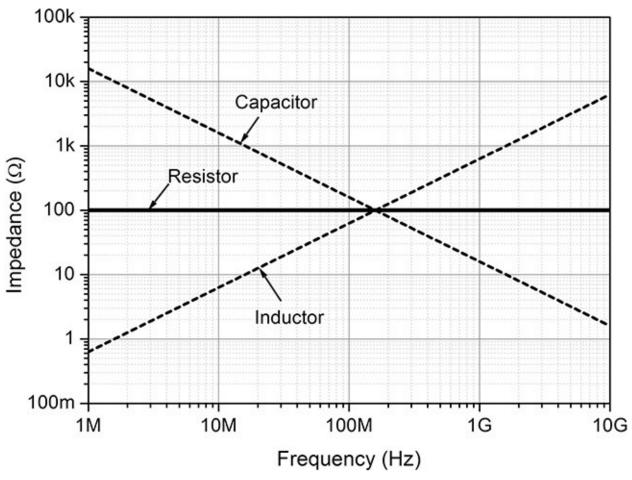

Figure 2.1 shows the log-log scale plot of |Z| in the equations above. In the case of a resistor, it exhibits constant impedance independent of frequency, while the impedance of a capacitor linearly decreases, and that of an inductor increases with frequency, as shown in Figure 2.1. There are various ways of fabricating capacitors, and inductors, which produce similar impedance characteristics for some limited ranges of frequency. In this chapter, we will examine how the passive devices are classified based on their fabrication methods, and we will look at the impedance characteristic dependence on fabrication methods. Commercially available resistors, capacitors, and inductors generally exhibit the impedance characteristics shown in Figure 2.1 at low frequencies; however, they generally do not have the simple and ideal characteristics described above as the frequency increases. The impedance characteristic typically becomes more complicated at higher frequencies and it is necessary to examine the characteristics before circuit design. In practice, complicated equivalent circuits are needed for their representations as the frequency increases, which adds to the difficulty and complexity of circuit design at high frequencies.

**Figure 2.1** Impedance plots of a 100  $\Omega$  resistor, a 10 pF capacitor, and a 100 nH inductor

In such circumstances, the equivalent circuit that properly reflects the impedance characteristics in the frequency range of operation should be used in circuit design. The critical factors will be the *understanding of the typical equivalent circuit of such commercially available resistors, capacitors and inductors*, and *the technique to determine the equivalent circuit values with given data*. Typical forms of data are available as a datasheet and library in design software. When data are not available, measurements or EM simulations can be carried out to determine them. Therefore, in this chapter, detailed data analysis techniques and appropriate measurement techniques in the absence of data will be discussed.

## 2.2 Classification

Largely based on their fabrication method, passive devices are classified into *lead-type* and *chip-type* components, and *pattern-type* passive components. Lead-type and chip-type components are widely available commercially. Photographs of them are shown in <u>Figure 2.2</u> and <u>Figure 2.3</u>, respectively. Pattern-type passive components are formed by patterns on substrate.

**Figure 2.2** Lead-type components: (a) resistor, (b) capacitor, and (c) inductor

**Figure 2.3** Chip-type components: (a) resistor, (b) capacitor, and (c) inductor

The assembly method of lead-type and chip-type components differs. While lead-type components are basically assembled using an *insertion technique*, chip-type components are assembled using a *surface mounting technique*. In

assembling a lead-type component, the lead terminals are first bent and inserted into through holes formed in the printed circuit board. The unnecessary lead terminals are then cut and the printed circuit board with lead-type components is dipped into melted solder, and finally the lead terminals are soldered to the round conductor patterns formed around the through holes on the bottom side of the PCB. In the case of chip-type components, solder creams are first printed to land patterns formed on a printed circuit board or substrate, and chip-type components are mounted on the land patterns manually or automatically. Finally, passing through a reflow machine with an appropriate temperature profile, the soldering of chip-type components to the land patterns is completed. In the case of lead-type components, it should be noted that the lead terminals are supposed to be used only for connections. However, they also give rise to parasitic inductance at high frequencies, and consequently the impedance of the remaining lead terminal adds to the impedance of the passive device. In the past, these lead-type components were mostly used as passive devices before chiptype components became commercially popular. But due to the fluctuations arising from the length of the lead terminals when assembled, lead-type components are seldom used at high frequency although they are still used for low-frequency applications. In addition, lead-type components are generally bigger than chip-type components.

Compared to lead-type components, chip-type components have relatively fewer parasitic elements caused by the terminals, which becomes advantageous at high frequencies. However, the key reason for the popularity of these devices is miniaturization rather than their advantage for use at high frequencies. In addition, the surface-mounting technique, which provides an advantage in large-scale fabrication, is another reason why they are widely used.

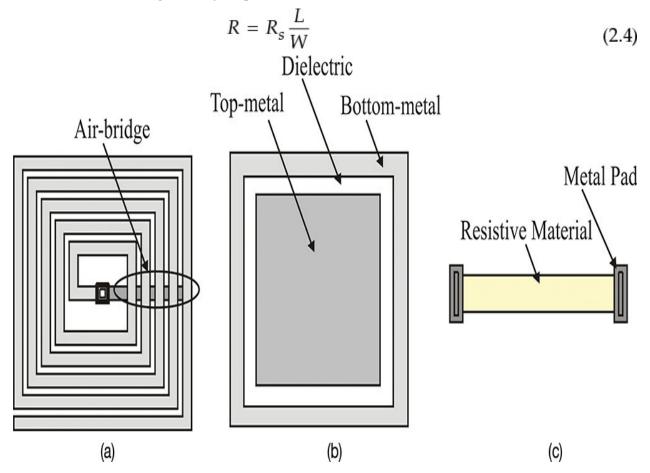

Pattern-type passive components can usually be produced on the substrate by using the process of a monolithic microwave integrated circuit (MMIC) or thin film in situations where a circuit designer directly creates passive devices through the use of patterns. However, there are limits to the range of values attainable with this method compared to chip-type or lead-type components, which is a disadvantage.

In the case of a resistor, as shown in Figure 2.4(c), a thin film of a resistive material (usually NiCr and TaN) is used as a resistor pattern on which the conductor pattern (for the purpose of connection) is formed by the appropriate technique. The resistor in Figure 2.4(c) has a uniform thickness and the resistance is thus proportional to the length (L) and inversely proportional to the

width (W). The proportionality constant is defined as the *sheet resistivity*  $R_S$ , and the resistance R is given by Equation (2.4).

**Figure 2.4** Passive components produced by pattern formation: (a) inductor, (b) capacitor, and (c) resistor

Note that  $R_S$  has the dimension of  $\Omega$ /square.

In the case of the capacitor in Figure 2.4(b), a uniform-thickness dielectric sheet is formed on the bottom conductor pattern, a top conductor pattern is again formed on the dielectric, and a metal-insulator-metal (MIM) capacitor is formed. The dielectric material's thickness, generally determined by the process, is constant and once the *sheet capacitance*  $C_S$  has been determined, the capacitance is then directly proportional to the surface area (A) and is expressed in Equation (2.5).

$$C = C_s A \tag{2.5}$$

Of course, as the frequency increases, the parasitic elements inherent in the MIM capacitor will appear, and will need appropriate modeling in the frequency range of operation.

In the case of an inductor, it is usually implemented as a spiral type, as shown in Figure 2.4(a). Its design is not as simple as that of a capacitor or resistor. Foundry-service companies usually provide measured results or data on several configurations of inductors. In the absence of this information, the values of inductors are determined through electromagnetic (EM) simulation. In addition, although the assessment of these pattern-type components is important, when viewed from a design point of view, the construction of their equivalent circuits is the same as that of chip-type or lead-type components, and so its specific discussion will be omitted here.

### Example 2.1

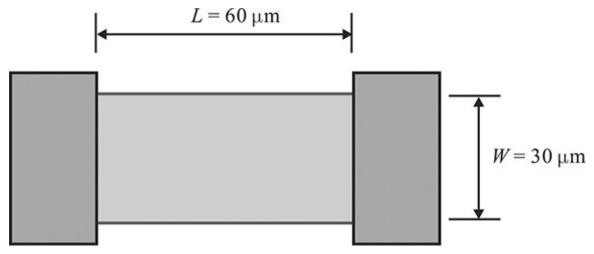

(1) Given that the sheet resistance  $R_S$  is 50  $\Omega$ /square, calculate the resistance of the component shown in Figure 2E.1 below.

Figure 2E.1 Resistor pattern

(2) The permittivity of an MIM capacitor is 7.2 and its thickness is 0.4  $\mu$ m. Determine the sheet capacitance in pF/mm<sup>2</sup> and then calculate the capacitance of a 50  $\mu$ m<sup>2</sup> capacitor.

#### **Solution**

(1) In the case of the resistor, since the value of the sheet resistance  $R_S$  is 50  $\Omega$ /square, then

$$R = R_{\rm S} \frac{L}{W} = 50 \times \frac{60}{30} = 100 \,\Omega$$

(2) In the case of the capacitor, the sheet capacitance per square mm is

$$C_S = \varepsilon_r \varepsilon_0 \frac{A}{t} = 8.854 \text{ pF/m} \times 7.2 \times \frac{1 \text{ mm}^2}{0.4 \text{ }\mu\text{m}}$$

= 8.854 pF/m × 7.2 ×  $\frac{1 \text{ m}}{0.4}$  = 159 pF

Thus,  $C_S$  = 159 pF/mm<sup>2</sup> and for a capacitor having an area of 50  $\mu$ m × 50  $\mu$ m, the capacitance is

$$C = C_S \times 0.05^2 = 159 \times 0.05^2 \text{ pF} = 0.398 \text{ pF}$$

# 2.3 Equivalent Circuits

As mentioned earlier, pattern-type passive components require the thin-film or MMIC process. When pattern-type components are not used, the most likely choice for passive components in high-frequency applications is chip-type components because lead-type components are not appropriate for higher-frequency applications. In this section, the methods for manufacturing and evaluating chip-type components will be explained. In addition, the method for extracting the equivalent circuit from given data will be described.

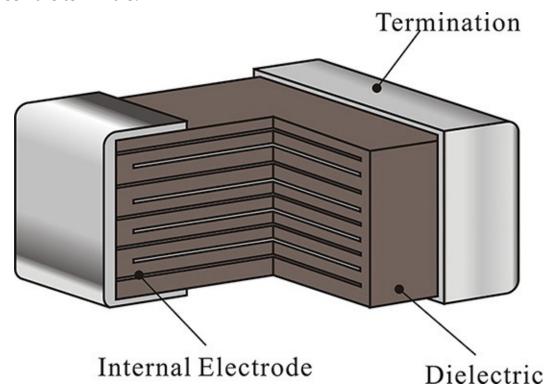

## 2.3.1 Chip-Type Capacitors

A chip-type capacitor is usually constructed using a multilayered structure, as shown in Figure 2.5. Each terminal consists of a number of parallel conducting plates (in Figure 2.5, they are labeled as internal electrodes), and the sum of the capacitance formed between the parallel conducting plates appears at the terminals of the chip-type capacitor. The dielectric fills the space between the conducting plates and its dielectric constant further increases the capacitance between the terminals.

Figure 2.5 Structure of a chip capacitor. The capacitance appears at the two

terminals and is the sum of the capacitance appearing between two nearby conducting plates. Using high-permittivity ceramic material, the capacitance can be increased.

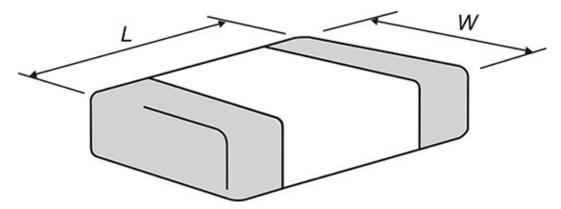

The classification of chip-type capacitors is based on the geometrical parameters shown in Figure 2.6: length L between the terminals and terminal width W. Based on a standard unit of mm, a capacitor having a length of 1.0 mm and a width of 0.5 mm is called type 1005; following a similar definition, type 1608 is a capacitor that has a length of 1.6 mm and a width of 0.8 mm. This classification is not limited to capacitors; resistors and inductors are classified in the same way. Thus, a 1608 resistor represents a chip resistor with a length of 1.6 mm and a width of 0.8 mm.

**Figure 2.6** Dimensions of a chip-type component (*L*: length, *W*: width)

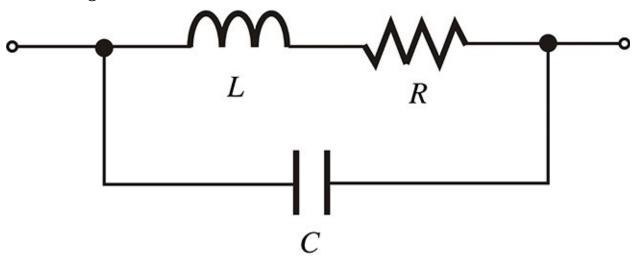

The impedance of such a capacitor depends on the frequency and the general equivalent circuit as shown in Figure 2.7. In that equivalent circuit, C represents the capacitance of a chip capacitor, L is the parasitic inductance that appears due to the multilayer structure, and R represents the loss in the dielectric material used in the capacitor. Therefore, from a structural point of view, as the size of the capacitor becomes smaller, inductance L generally becomes smaller. It should also be noted that the inductance generally tends to be constant regardless of the value of the capacitance when the size of the chip-type capacitor is equal.

*C*: capacitance of the capacitor

*L*: parasitic inductance (0.7 nH–1 nH)

*R*: represents the loss of the conductor plate

**Figure 2.7** The equivalent circuit of a chip-type capacitor. C is the value of the capacitor and L occurs due to conductor patterns used to form the capacitor. R is due to the conductor and dielectric losses.

Figure 2.8 shows the impedances of chip-type capacitors with respect to frequency. Looking at the 100 pF curve in the figure, a frequency of about 100 MHz, the impedance decreases linearly with frequency. This is obvious because at low frequency the chip capacitor behaves as an ideal capacitor. Since it shows an impedance of about 30  $\Omega$  at 50 MHz, it can be seen to have a capacitance of

an impedance of about 30  $\Omega$  at 50 MHz, it can be seen to have a capacitance of  $C = \frac{1}{2\pi f X_c} \cong \frac{1}{2\pi \times 50 \times 10^6 \times 30} = \frac{1000}{2\pi \times 1.5} \text{ pF} \cong 106 \text{ pF}$ 100 1 pF 10 pF 100 pF 10 1000 pF Impedance (Ω) 1 0.1 10M 100M 10G 1M 1G

Figure 2.8 Impedance characteristics of GRM36 series chip-type capacitors

Frequency (Hz)

### (refer to the datasheet<sup>1</sup>)

1. Murat Manufacturing Co. Ltd., Chip Monolithic Ceramic Capacitor, 1999.

The error in the calculated capacitance value is due to the approximate reading of the impedance value from the graph. From Figure 2.8, as the frequency increases, the impedance, after reaching a minimum, rises again. This can be understood from the equivalent circuit of the chip-type capacitor in Figure 2.7. While the impedance of capacitor C in Figure 2.7 is decreasing, that of inductor L is increasing with frequency. Thus, as the frequency increases, inductor L in Figure 2.7 becomes dominant, which explains why the impedance of the chip-type capacitors shown in Figure 2.8 increases with frequency.

From the minimum point of the 100 pF curve in Figure 2.8, series resistance R in the equivalent circuit of Figure 2.7 is found to be approximately 0.2  $\Omega$ . Furthermore, at a frequency of 1 GHz, assuming that the impedance is mainly determined by an inductor, the approximate value of the inductor can be obtained from the curve. Since its impedance is approximately 5  $\Omega$  at 1 GHz, the approximate inductance value is found to be  $L = \frac{X_L}{2\pi f} \cong \frac{5}{2\pi \times 1 \times 10^9} = \frac{5}{2\pi} \text{ nH} \cong 0.8 \text{ nH}$

More accurate values of the equivalent circuit can be determined by curve fitting, which is widely used to fit such data.

Thus, in the case of the 100 pF capacitor, when used at a frequency of over 1 GHz, it acts as an inductor rather than a capacitor. In order to use the 100 pF capacitor as a DC block, it must have, at most, an impedance below 5  $\Omega$  (which is estimated as 1/10 of a standard impedance value of 50  $\Omega$ ). From the graph in Figure 2.8, it is possible to use the 100 pF capacitor as a DC block or a bypass capacitor in the frequency range of 300 MHz to 900 MHz. Its use as a DC block at a higher frequency poses a difficulty due to the effect of the parasitic inductor.

## 2.3.2 Chip-Type Inductors

The manufacturing methods of chip-type inductors are somewhat more diverse when compared to those of chip-type capacitors. The structures of chip inductors vary, depending not only on their manufacturing methods but also on their values, DC current limits, and frequency coverage. Thus, the structures are not shown here and readers should refer to the datasheet. Basically, an inductor is formed by winding *enamel-coated copper wire* on either a ferrite core or dielectric materials. The enamel-wire winding is sometimes replaced by thick-film printing technologies. After the inductor is formed by winding, appropriate

solder terminals for connections are made. More winding is possible with a wire of thinner diameter. The inductance can be significantly increased by increasing the number of windings. However, it should be noted that this will lead to increasing series resistance and decreasing current capacity. In addition, this will also lead to a proportional increase of parasitic capacitance. Therefore, the inductor with a larger inductance value usually cannot be used at high frequencies. Consequently, when inductors are employed in designing a circuit, the datasheet should be carefully consulted in order to determine the frequency range of operation. Since the inductor generally shows a parallel resonance due to parasitic capacitance, the inductor can be used as a resonator. However, the *Q* of the parallel resonance is generally low. Thus, when applied as a resonator to an oscillator, for example, a close examination of the datasheet for the *Q* value is required.

Figure 2.9 shows a typical equivalent circuit of a chip-type inductor where *L* represents the inductance arising from the winding, *R* represents the winding resistance, and *C* represents the sum of parasitic capacitances appearing between the windings.

**Figure 2.9** Equivalent circuit of an inductor. L is the value of inductor and C represents stray capacitance between the winding. R represents the winding-coil loss.

In Figure 2.9, at an extremely low frequency the chip-type inductor acts like a resistor R. As the frequency increases, the impedance of L in the figure becomes dominant and it acts as an inductor. As the frequency increases further, the impedance of C in the figure becomes smaller and then the inductor behaves as a capacitor. Thus, the approximate frequency range for the chip-type inductor in Figure 2.9 to be used as an inductor is shown in Equation (2.6).

$$\frac{R}{L} < \omega < \frac{1}{\sqrt{LC}} \tag{2.6}$$

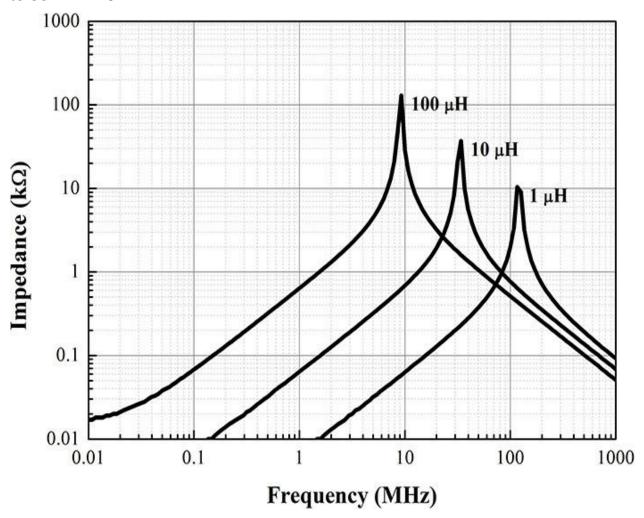

Figure 2.10 shows the impedances of chip-type inductors with respect to frequency. In this figure, examining the 100  $\mu H$  curve, it is found that the impedance increases linearly with frequencies up to 10 MHz. Thus, below 10 MHz, the chip-type inductor behaves as an inductor. Since the impedance value at 1 MHz appears to be approximately 0.6 k $\Omega$ , the inductance value is computed

to be

$$L = \frac{X_L}{2\pi f} \cong \frac{0.6 \times 10^3}{2\pi \times 1 \times 10^6} = \frac{0.6}{2\pi} \text{ mH} = 95.4 \text{ }\mu\text{H}$$

**Figure 2.10** Impedance characteristics of IMC1210 series chip-type inductors (refer to the datasheet<sup>2</sup>)

2. Vishay Intertechnology, Inc., <a href="http://www.vishay.com/docs/34043/imc1210.pdf">http://www.vishay.com/docs/34043/imc1210.pdf</a>, 2012.

Due to the approximate reading of the impedance value from the graph, an error arises in the calculated inductance value. As the frequency increases, the

impedance begins to fall after reaching a maximum point, which is due to the influence of the parasitic capacitor in the equivalent circuit in <u>Figure 2.9</u>. Thus, as the frequency becomes much higher, the inductor acts as a capacitor.

Assuming that at a frequency of 100 MHz the impedance is mainly due to a capacitor, then because its impedance is approximately 0.5 k $\Omega$  at this frequency, the value of the capacitor is computed to be  $C = \frac{1}{2\pi f X_c} \cong \frac{1}{2\pi \times 0.5 \times 10^3 \times 100 \times 10^6} = \frac{10}{2\pi \times 0.5} \text{ pF} \cong 3.2 \text{ pF}$

From Figure 2.10, the resistance at the maximum point (or parallel resonance) is 100 kΩ. The impedance value at this frequency becomes, approximately,  $\frac{\left(\omega_o L\right)^2}{R} = 100 \text{ K}$  and the value of the resistor in Figure 2.10 is  $\left(\omega_o L\right)^2 = \left(2\pi \times 10 \times 10^6 \times 100 \times 10^{-6}\right)^2$

and the value of the resistor in Figure 2.10 is

$$R = \frac{(\omega_o L)^2}{100 \text{ k}} = \frac{(2\pi \times 10 \times 10^6 \times 100 \times 10^{-6})^2}{100 \times 10^3} = 4\pi^2 \times 10 \approx 390 \,\Omega$$

## 2.3.3 Chip-Type Resistors

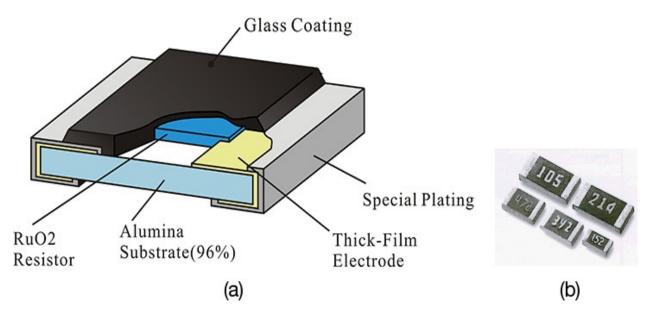

The structure of a chip-type resistor is shown in Figure 2.11(a), where the resistor is manufactured by printing a resistive material ( $RuO_2$ ) on a ceramic substrate. In addition, the terminals for connection are formed using a similar thick-film printed conductor pattern as shown in the figure. The thick-film printed terminals are plated to make soldering possible. Furthermore, in order to prevent oxidation or damage to the resistive material, a glassy coating is added to the resistive material in a post-processing application.

**Figure 2.11** Chip-type resistor; (a) structure and (b) photo. A chip-type resistor is formed by printing the resistive material using thick-film technology. A glass coating is applied for protection. The resistor's value is sometimes marked on the glass coating. Two digits represent the value of the resistor and the remaining digits represent the exponent. Thus, the three digits 342 stand for 3.4 k $\Omega$ .

A similar classification to that of capacitors (1005, 1608, and 2010) is also used in the classification of chip resistors. As the size of chip-type resistors gets smaller, similar to a capacitor the impedance characteristics generally become more ideal, that is, they can be applied to higher frequencies. Another factor to note is power consumption. The power consumption that a chip-type resistor can withstand is usually listed in the manufacturer's datasheet. The power consumption capability becomes generally smaller as the size of the resistor shrinks.

Depending on the manufacturer, the value of the resistor is sometimes marked on its surface, as shown in Figure 2.11(b), which makes the identification of that value much easier. In Figure 2.11(b), following a general notation, the first two digits represent the value of the resistance and the remaining digits represent the exponent. Thus, a 3.4 k $\Omega$  resistor is denoted as  $342 = 34 \times 10^2 = 3.4 \times 10^3 = 3.4$  k. The impedance characteristic with respect to frequency and the equivalent circuit of a chip-type resistor are not generally known. The method explained in the following section can be used for measuring the unknown impedance characteristic of a chip-type resistor. Using the measured impedance characteristic, the equivalent circuit of chip-type resistor may be found to be similar to chip-type capacitors and inductors.

# 2.4 Impedance Measurements

Chip-type passive components can all be considered as one-port components. Thus, using an *impedance analyzer* or a *network analyzer*, their impedance characteristics can be measured. Here, the method of measuring the impedance characteristics using the widely available network analyzer is presented. It should be noted that this method may be accompanied by significant errors when used with high frequencies.

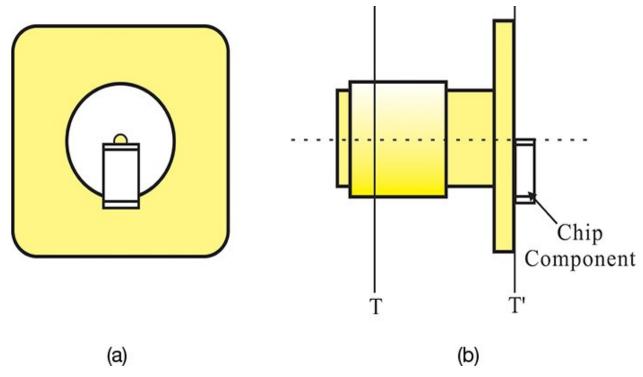

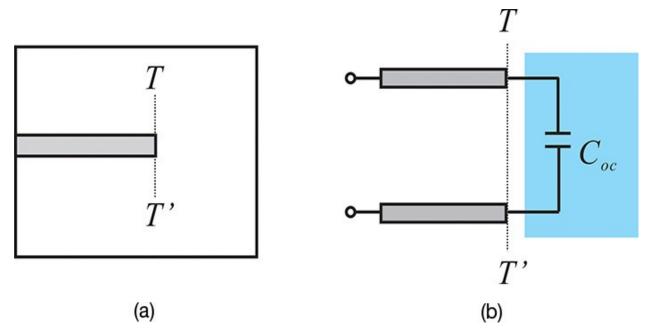

First, in order to perform measurements using the network analyzer, a coaxial small miniature assembly (SMA) connector must be prepared and its soldering tab (if present) should be removed, as shown in Figure 2.12. Next, the network analyzer should be calibrated with the one-port calibration procedure that is installed in the network analyzer. The calibrated reference plane appears at plane T in Figure 2.12. The calibrated reference plane T means that the measured impedance using the network analyzer includes all the effects of components connected after plane T. Here, for the time being, the calibration can be understood as the elimination of the non-ideal characteristics of the network analyzer and the movement of the measurement plane to plane T. In practical measurement, cables and adapters can be included for connecting the network analyzer to the assembly shown in Figure 2.12. Also, the network analyzer itself has the non-ideal characteristics. Without the calibration procedure, both the characteristics of cables and adapters and the non-ideal characteristics of the network analyzer are included in the measured impedance. Both of these effects can be removed through the calibration. After the calibration, the impedance can be correctly measured without the effects of cables and adapters and the nonideal characteristics of the network analyzer. After completing the one-port calibration, the calibrated reference plane appears normally at plane T of the connector.

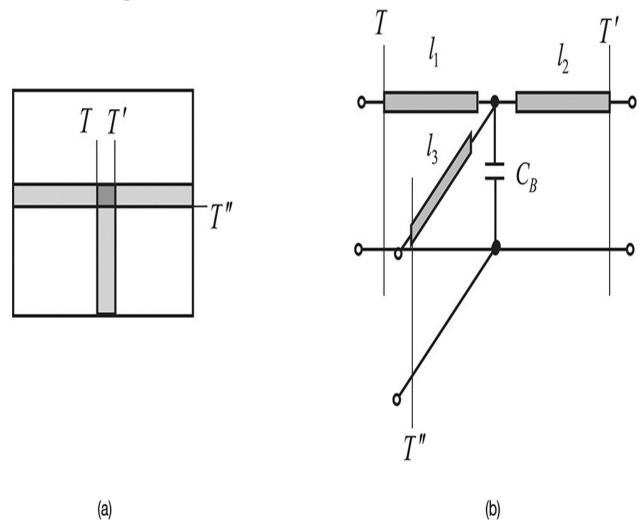

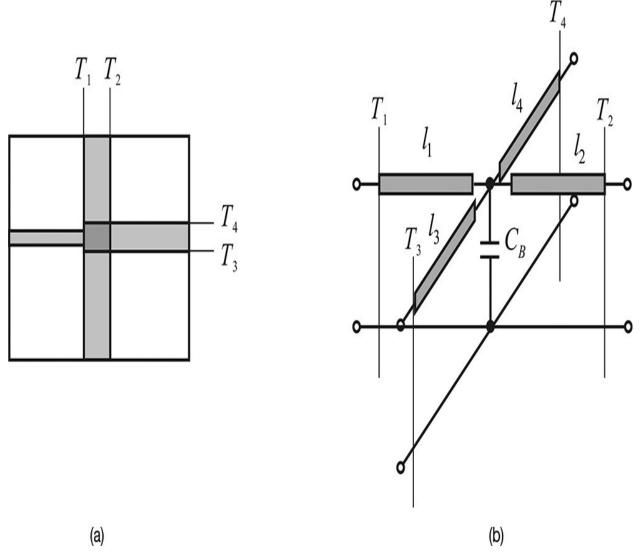

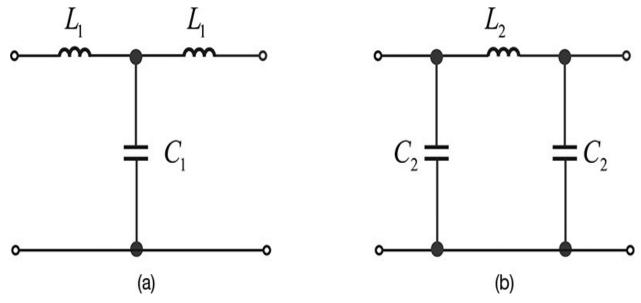

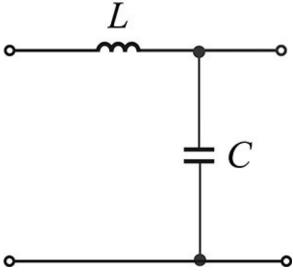

**Figure 2.12** Assembly for the measurement of a passive component; (a) back and (b) side views. Plane T is the conventional reference plane that appears after the completion of the network-analyzer calibration. The reference plane T can be moved to a new reference plane T' using electrical delay or port extension utilities.

The measured results at the calibrated plane T obviously include the length effect of the SMA connector, but the correct impedance of the passive component is defined at plane T'. Therefore, the length effect of the SMA connector should be removed from the measured impedance, which can usually be done by using the *electrical delay* or *port extension* function installed in the network analyzer. Since the measured impedance at plane T' in Figure 2.12 without the chip component should be  $\infty$ , it should be corrected to be open through the adjustment of the electrical delay. Now, the calibrated reference plane is moved to T'. The measured impedance based on this method may include some errors because such an open is not an ideal open.

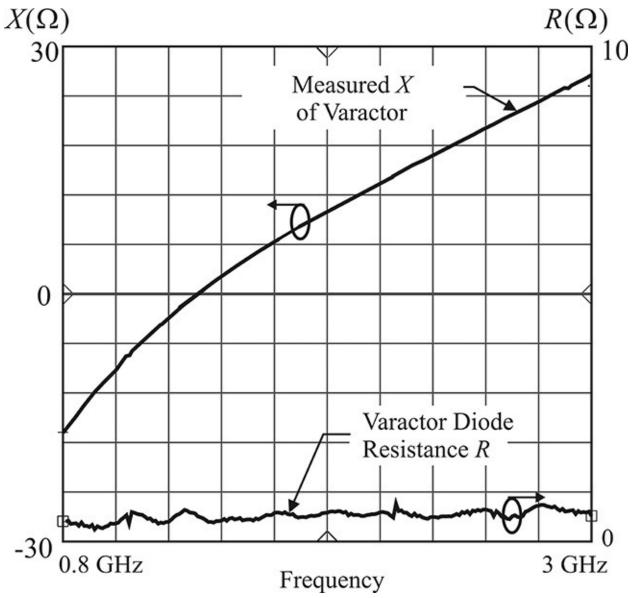

Next, the passive *device under test* (DUT) is connected by soldering the chip component to a connector, as shown in Figure 2.12(b). The measured impedance at plane T' corresponds to the impedance value of the chip component. Figure 2.13 shows an example of the measured impedance following the method presented. The DUT is a zero-biased varactor diode. The series resistance of the varactor diode is found to be approximately 0.5  $\Omega$ . At low frequency, the

measured reactance is negative and this implies that the varactor diode acts as a capacitor. However, as frequency further increases, the diode behaves as an inductor. Thus, the varactor diode can be modeled by the series resonant equivalent circuit in Figure 2.7. The values of R, L, and C can be determined through optimization.

**Figure 2.13** Measured impedance for a chip varactor diode using the method presented. The varactor diode can be modeled by a *RLC* series resonant circuit with a resonance frequency of about 1.4 GHz.

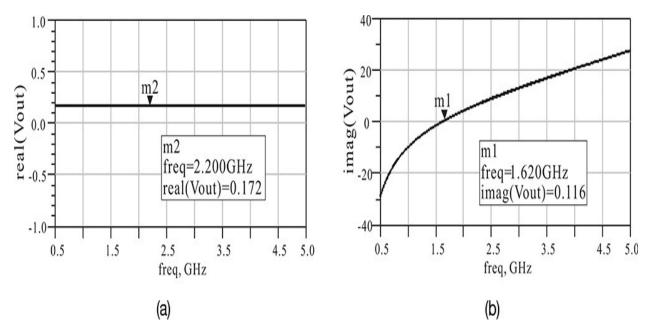

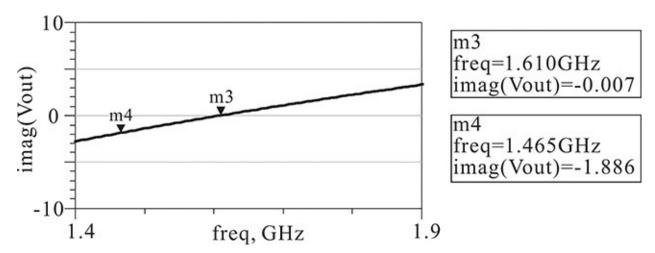

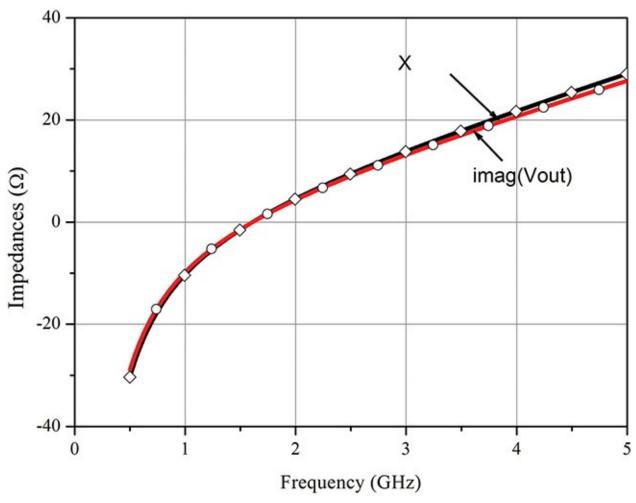

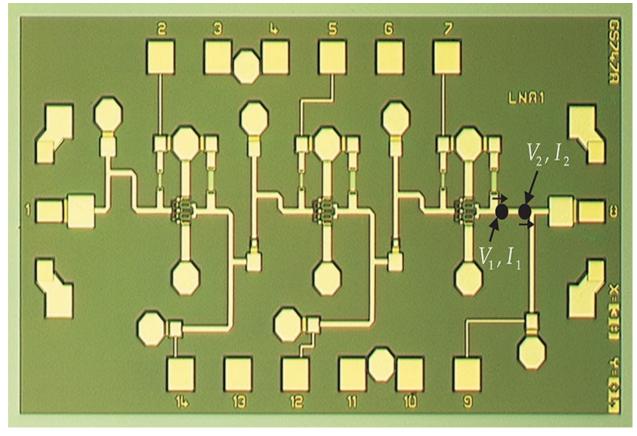

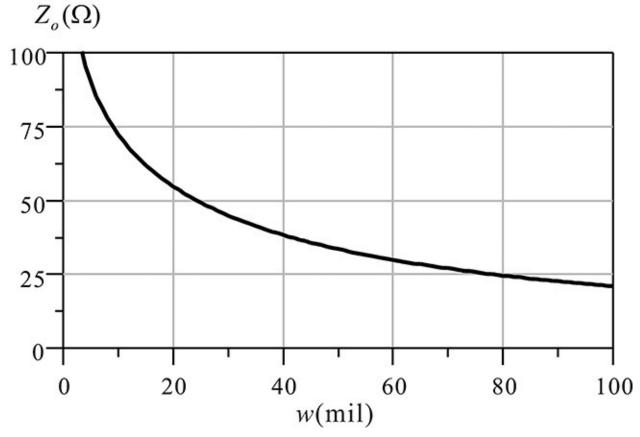

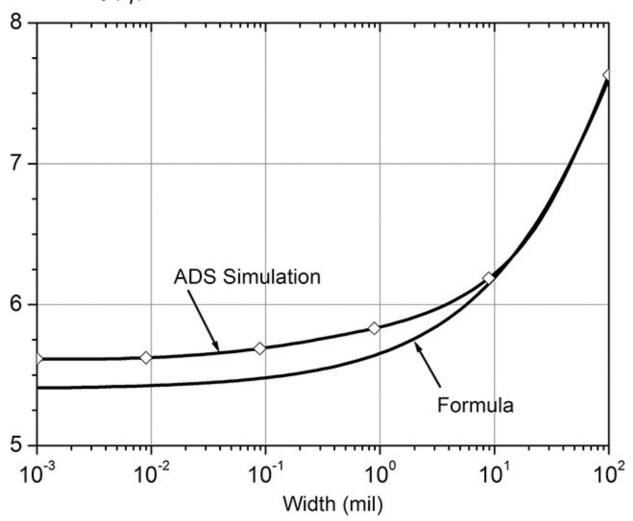

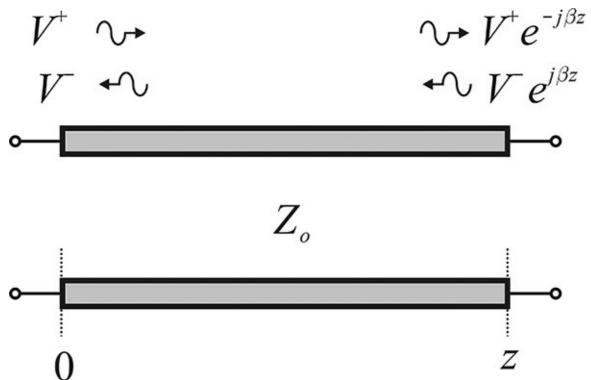

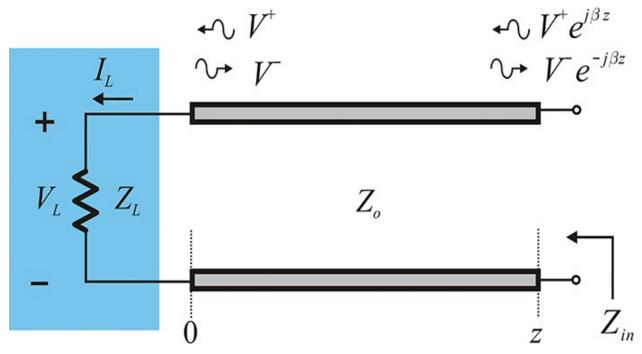

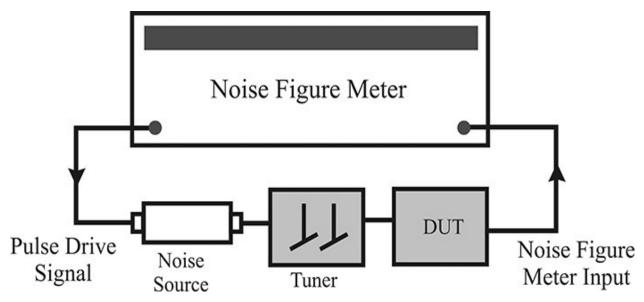

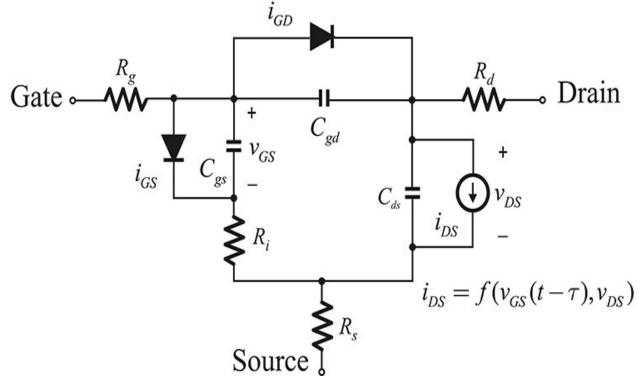

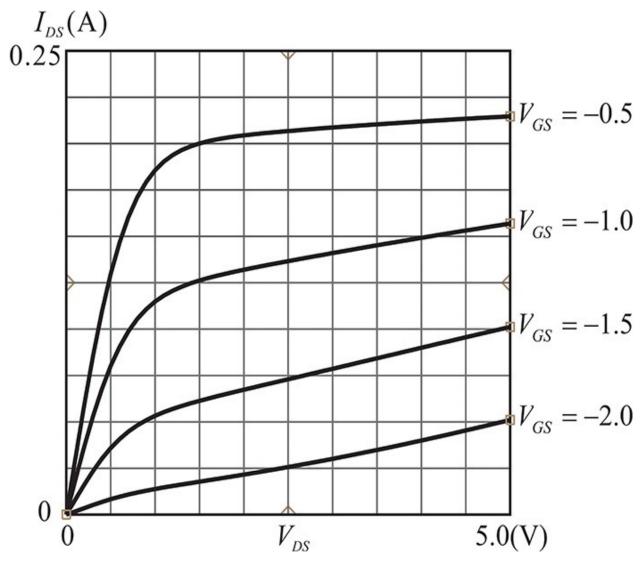

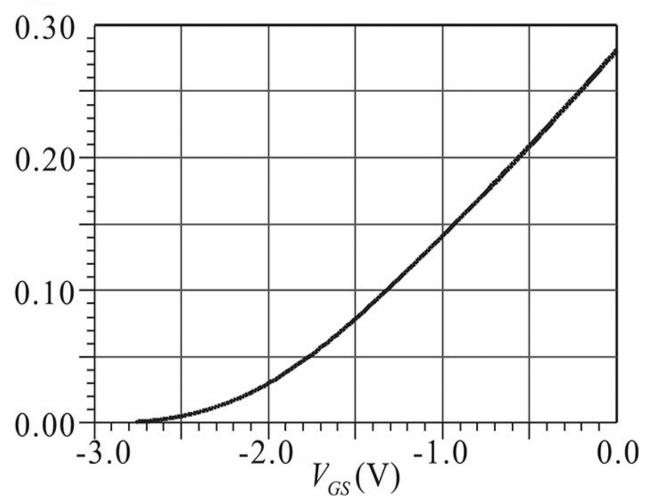

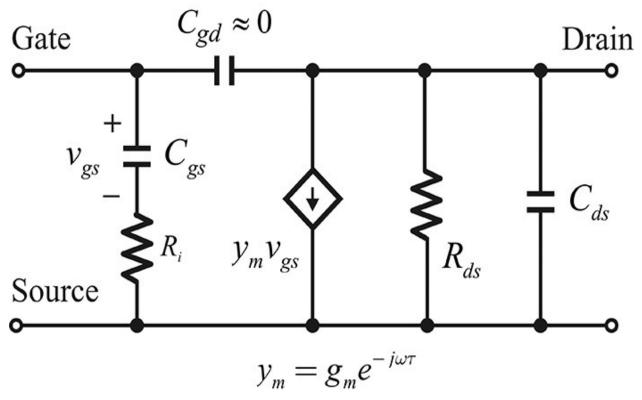

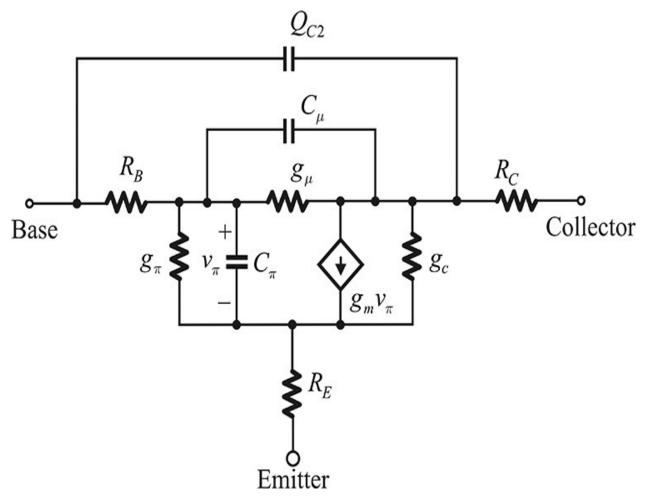

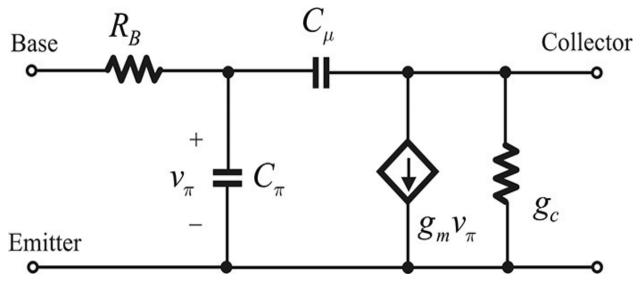

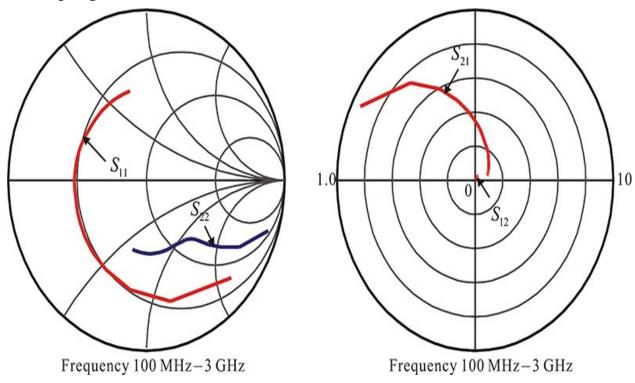

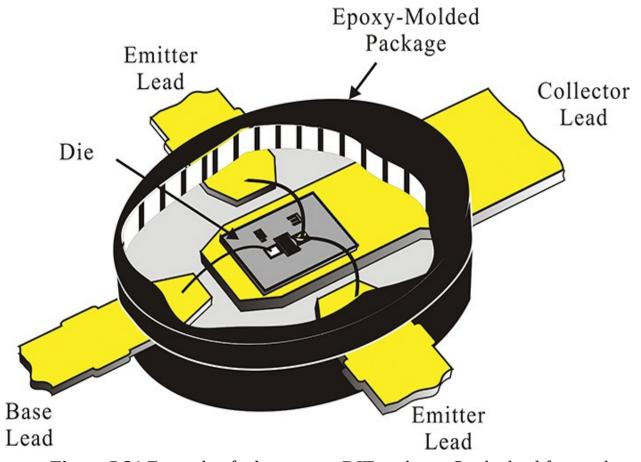

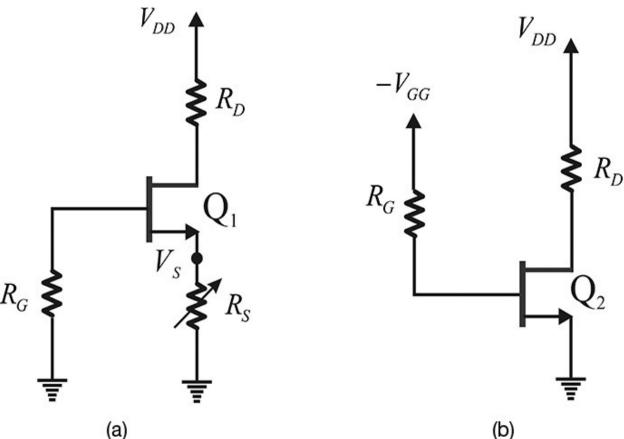

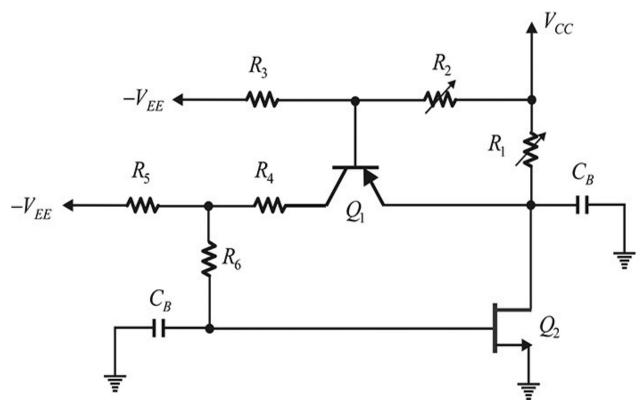

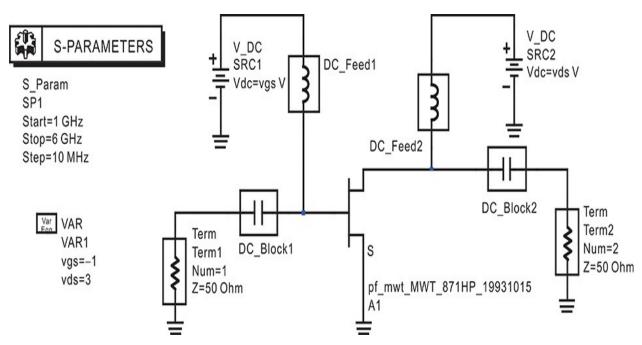

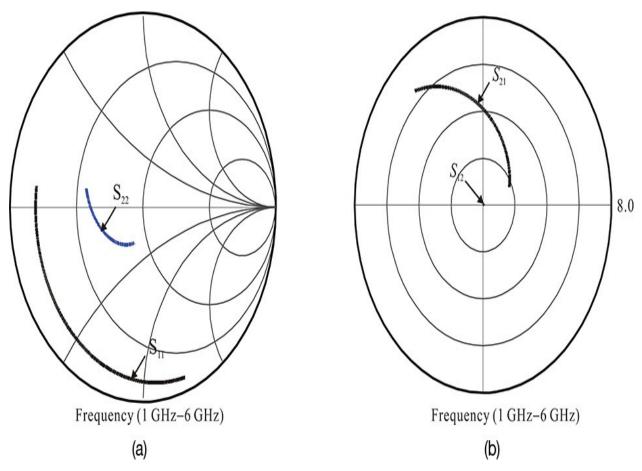

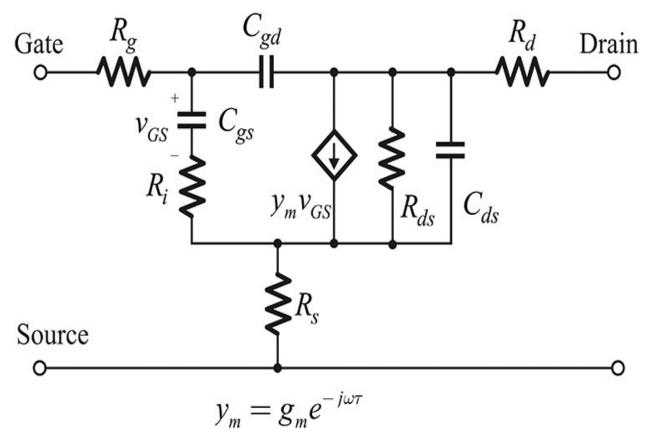

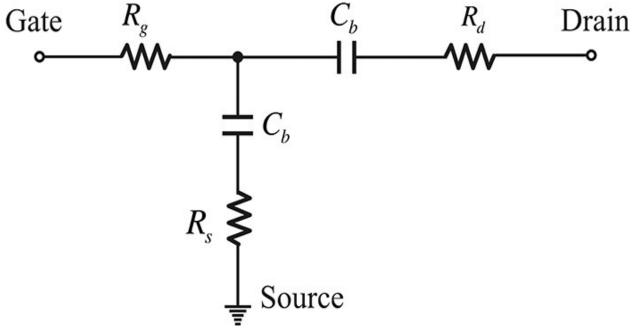

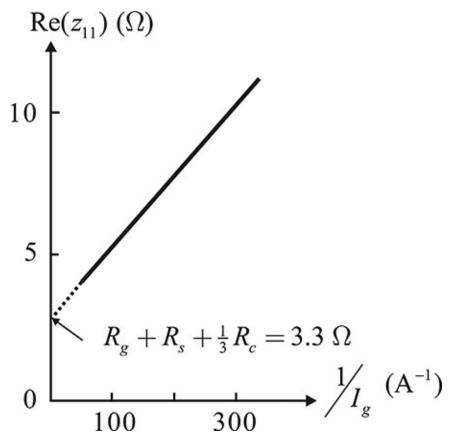

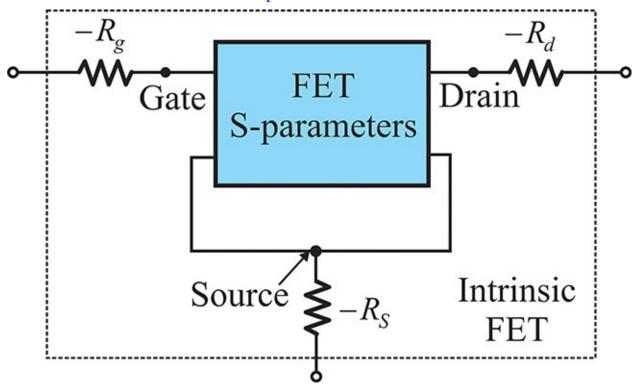

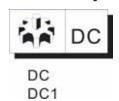

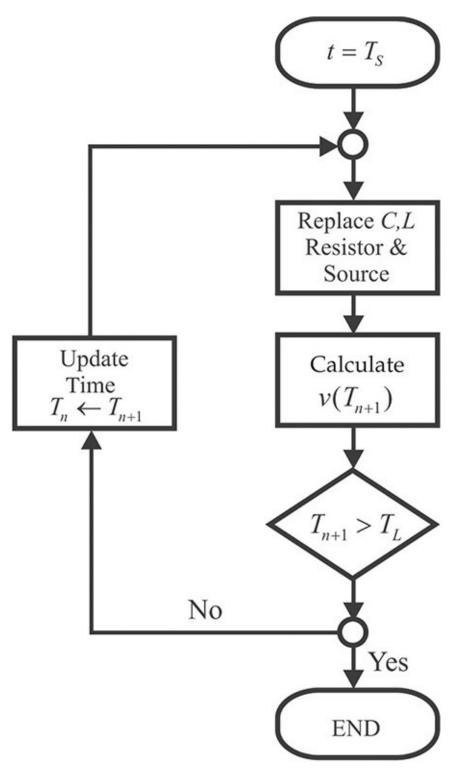

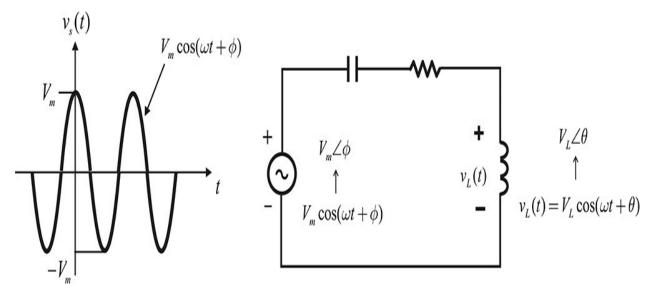

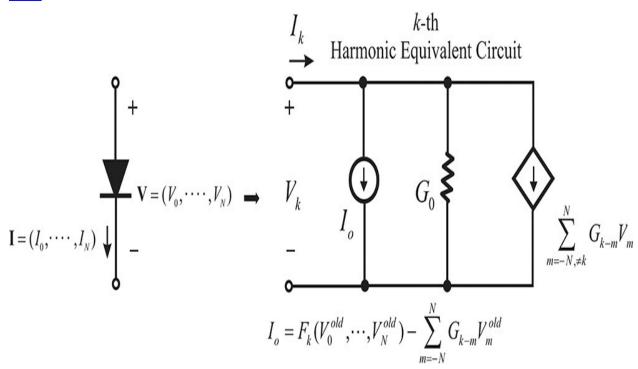

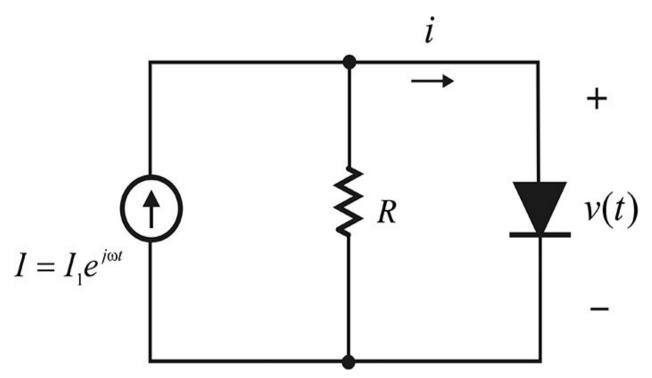

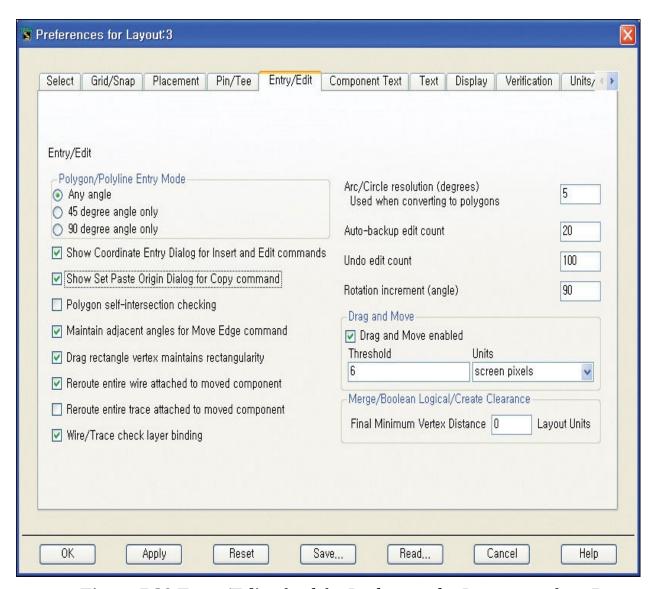

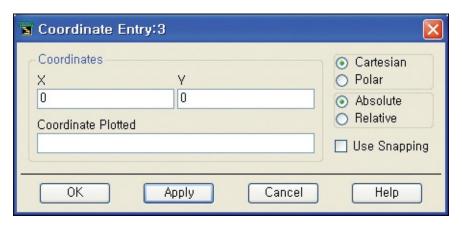

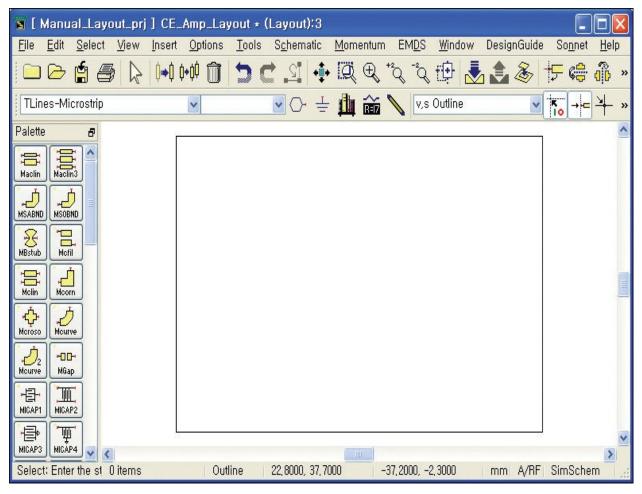

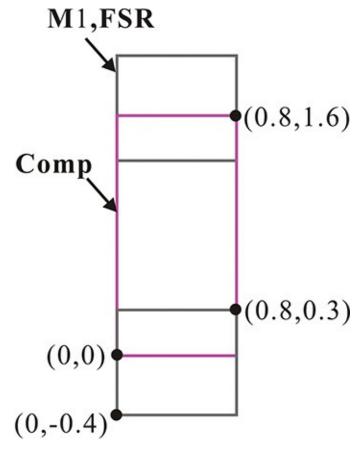

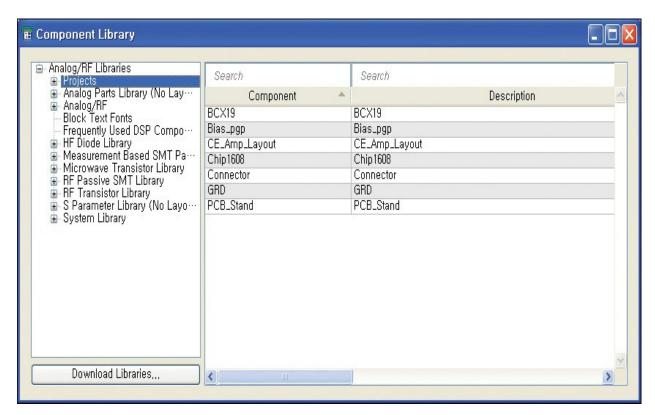

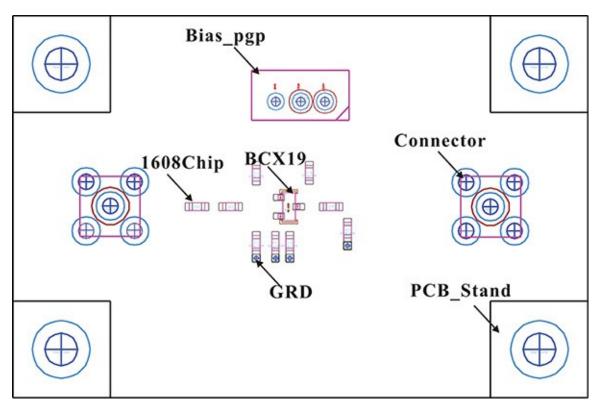

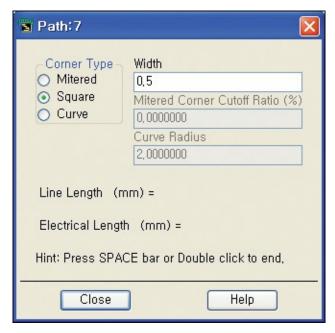

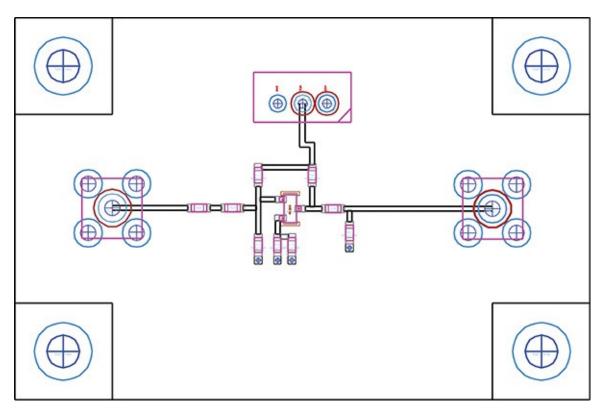

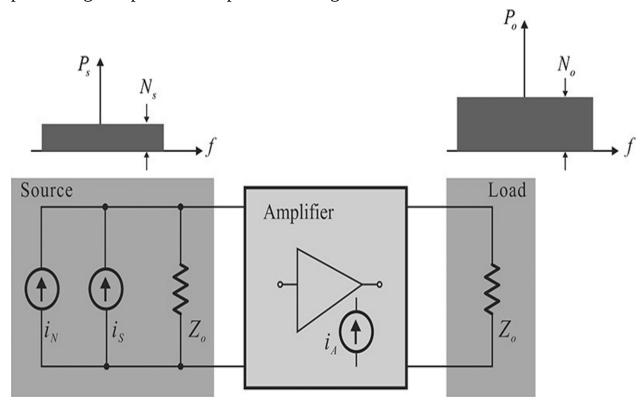

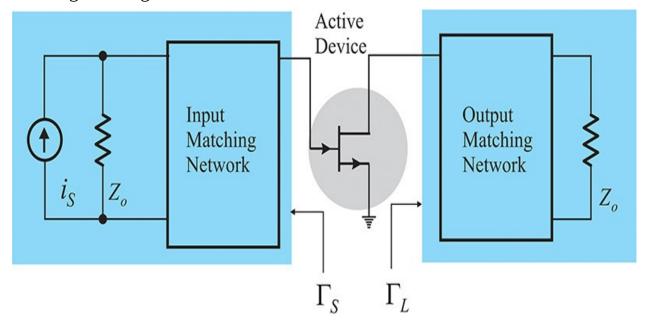

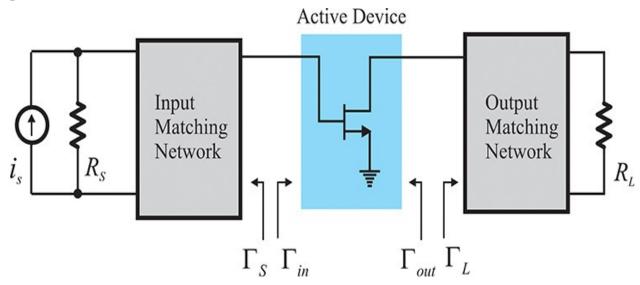

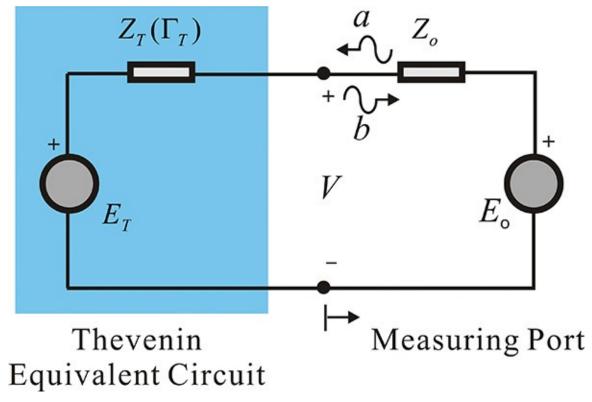

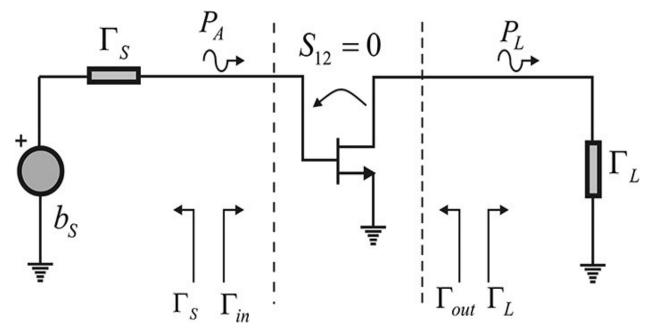

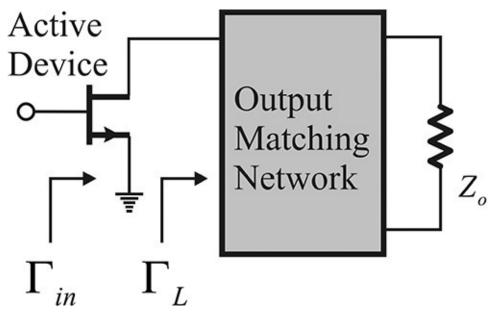

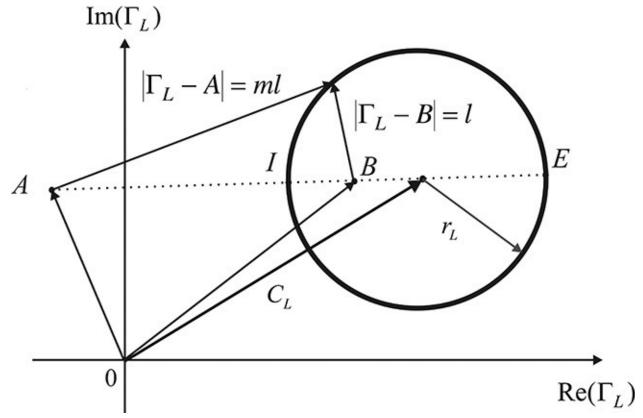

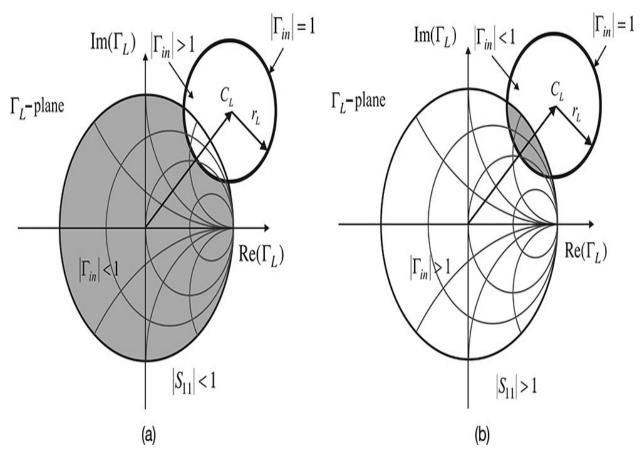

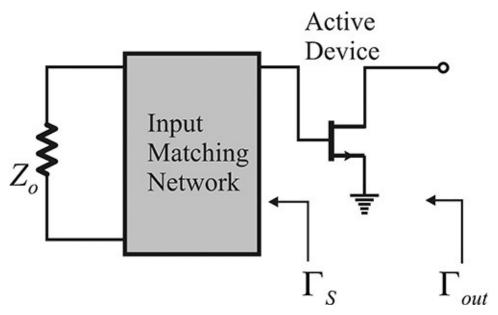

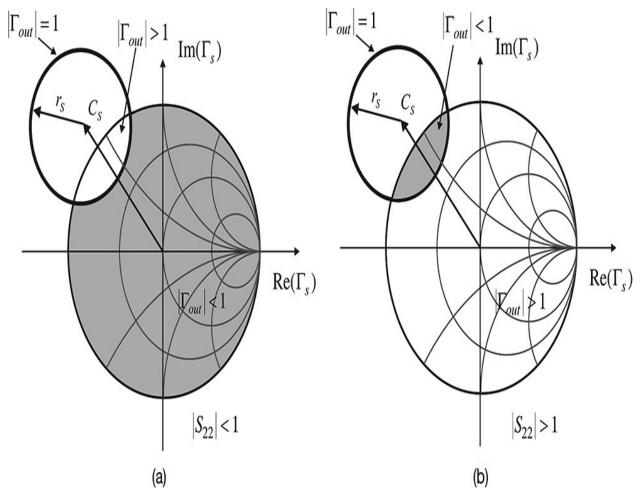

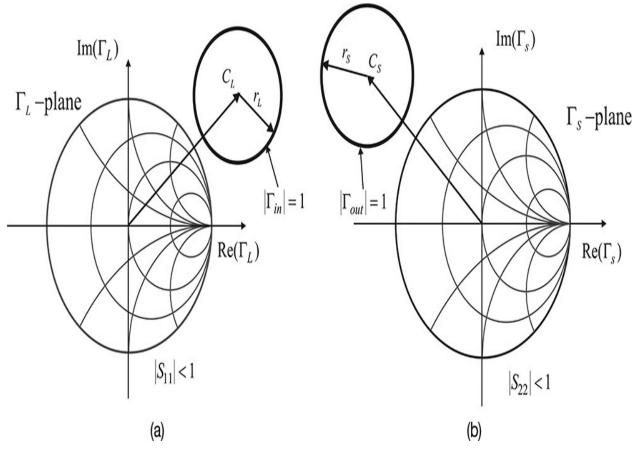

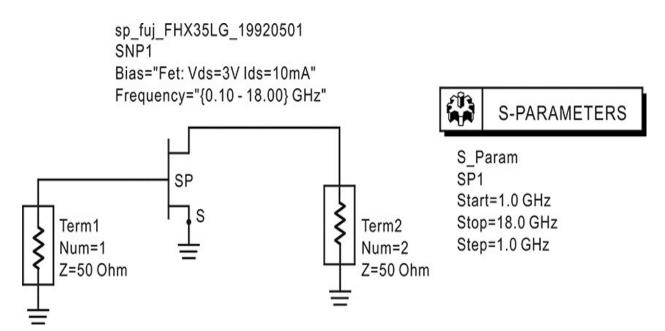

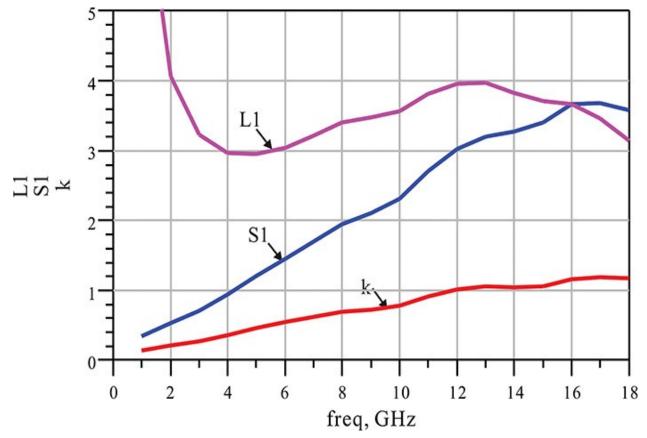

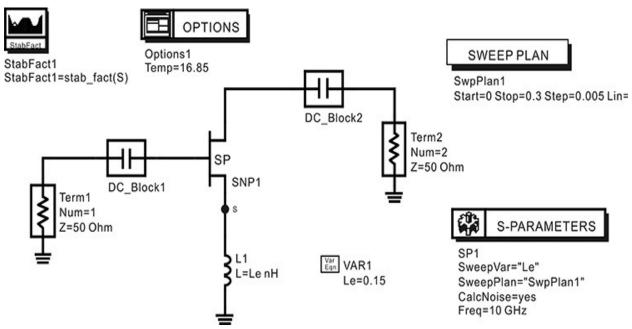

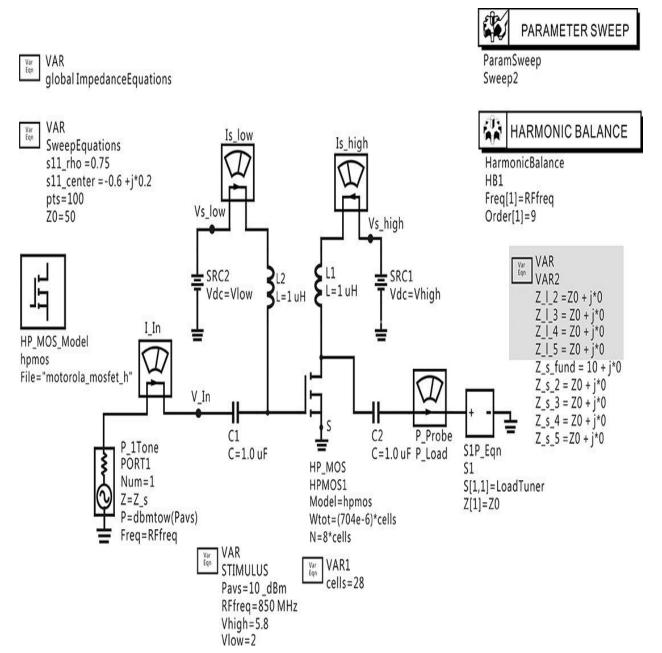

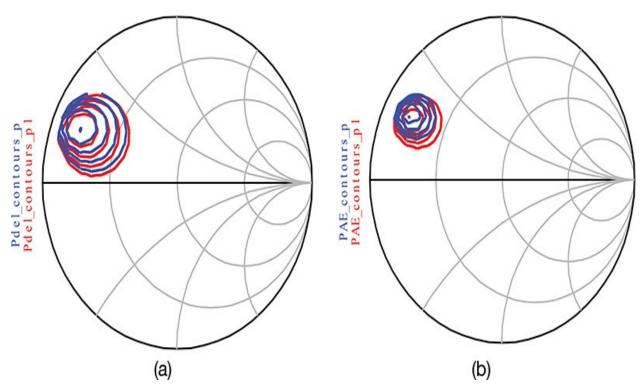

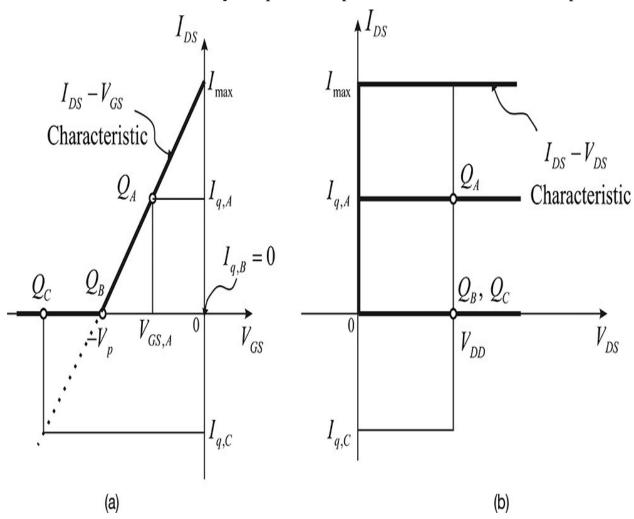

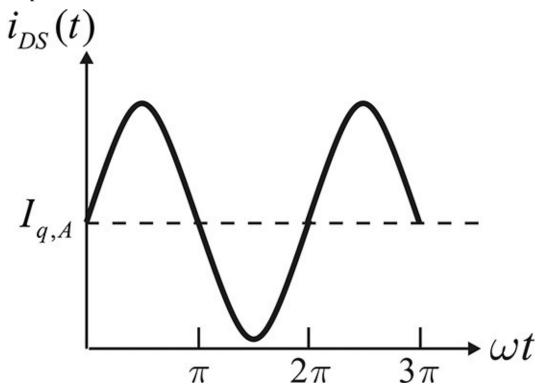

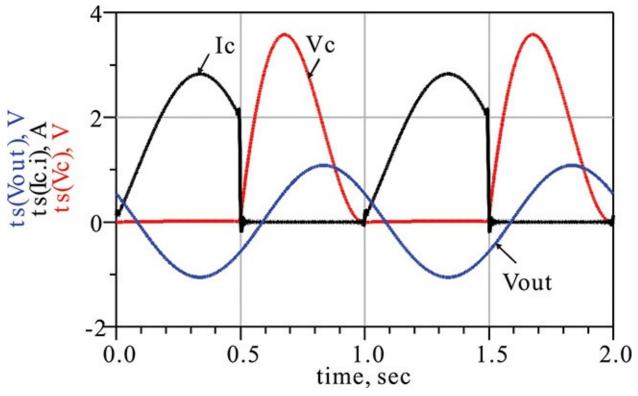

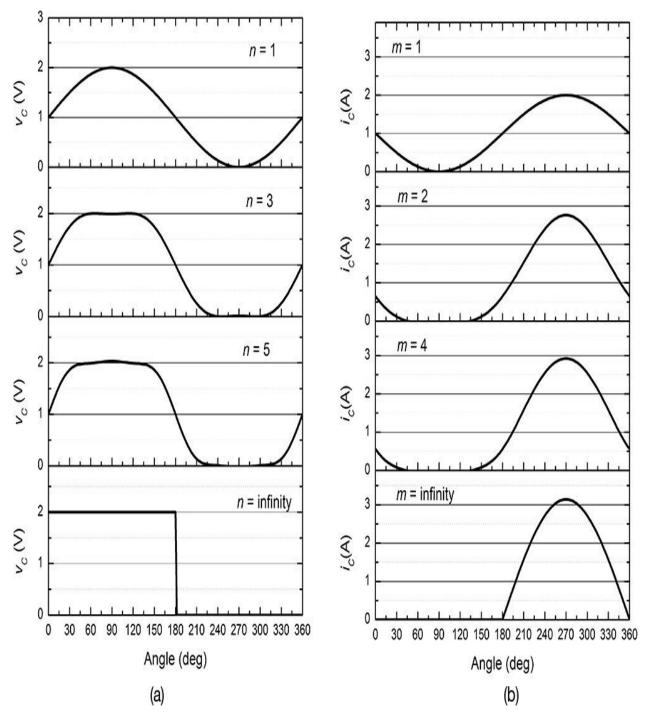

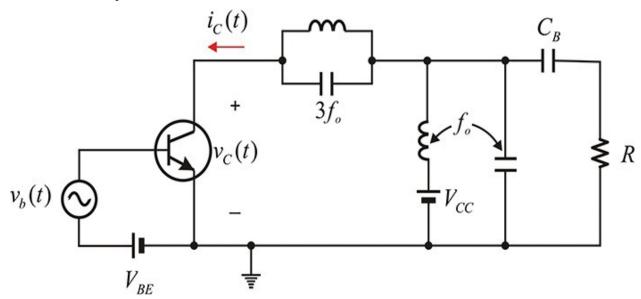

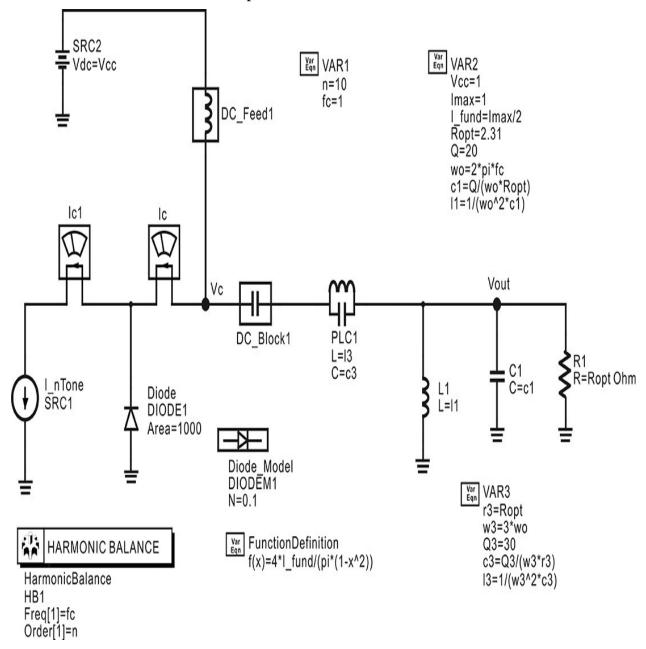

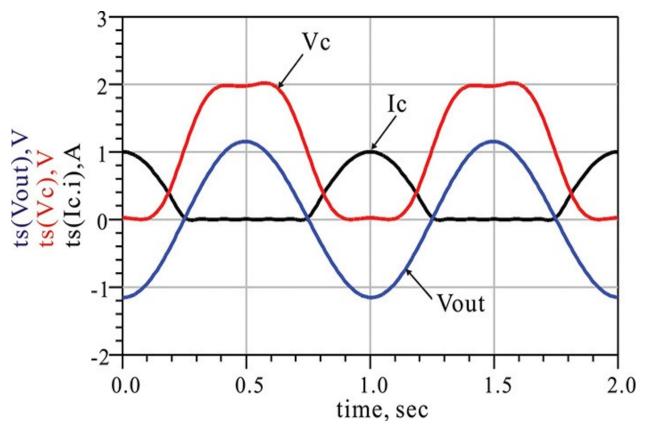

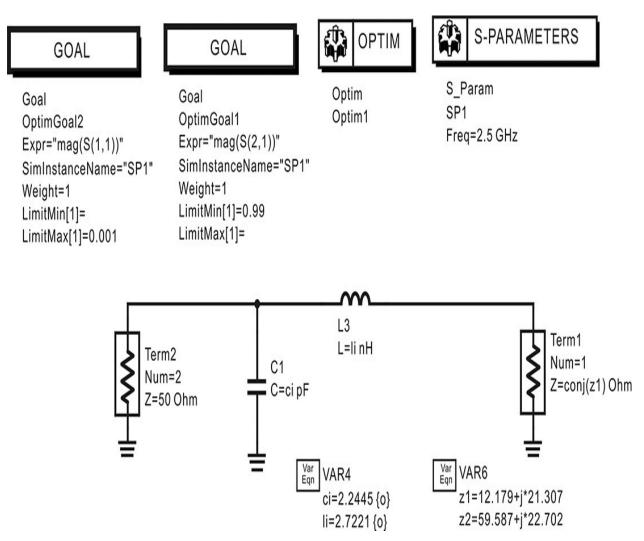

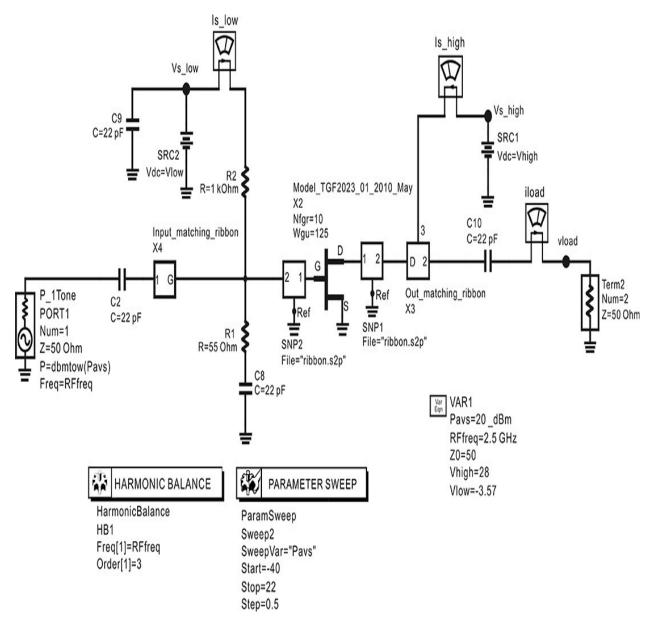

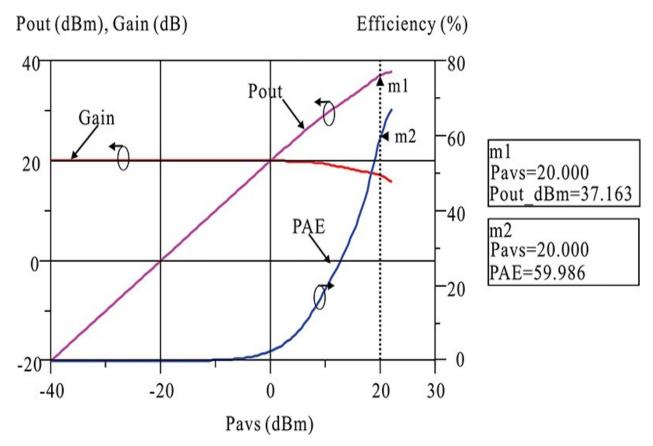

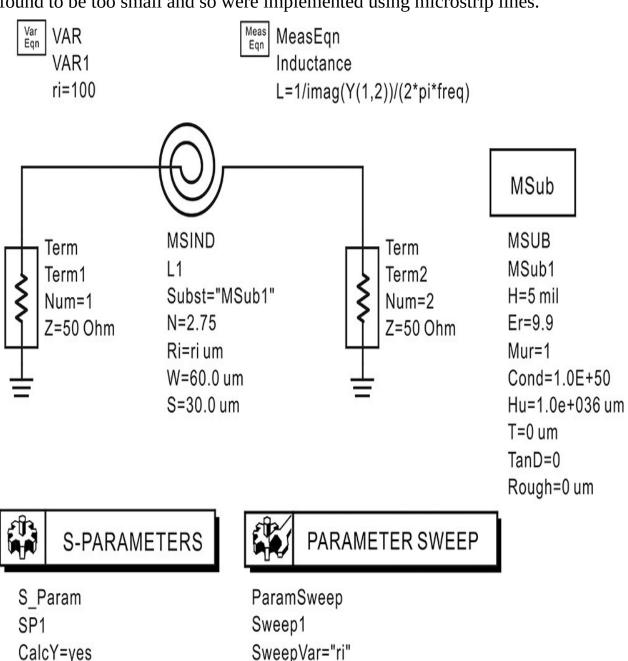

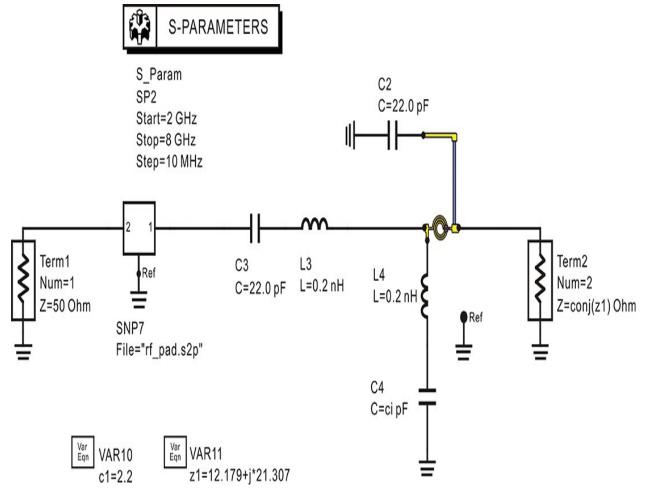

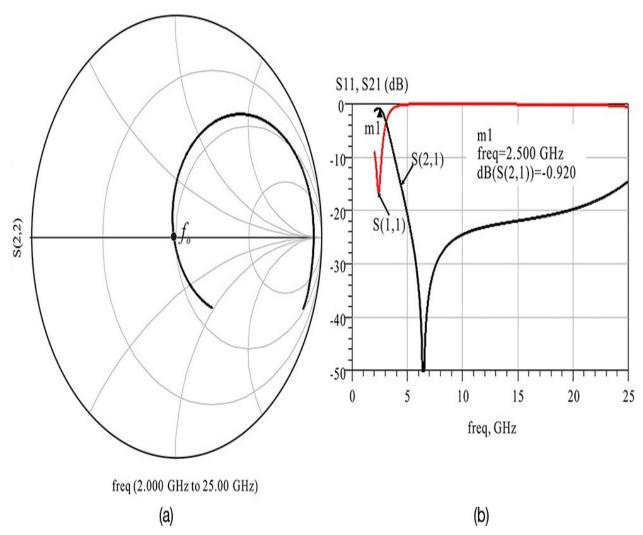

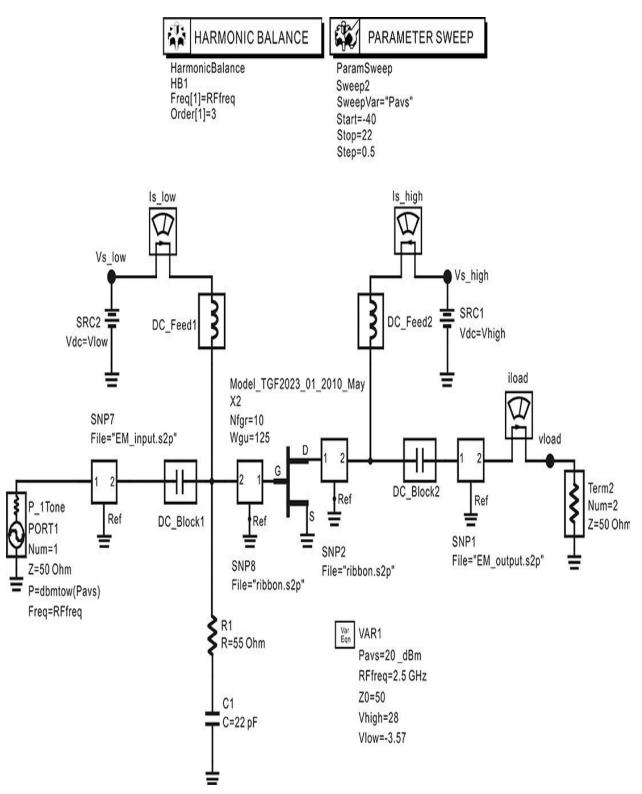

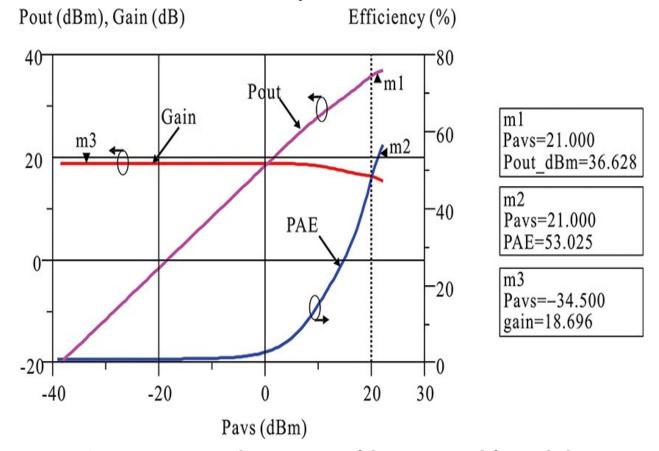

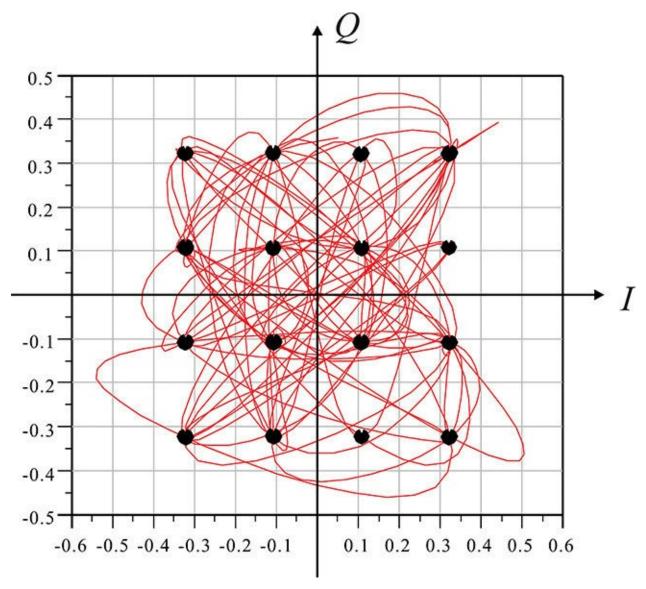

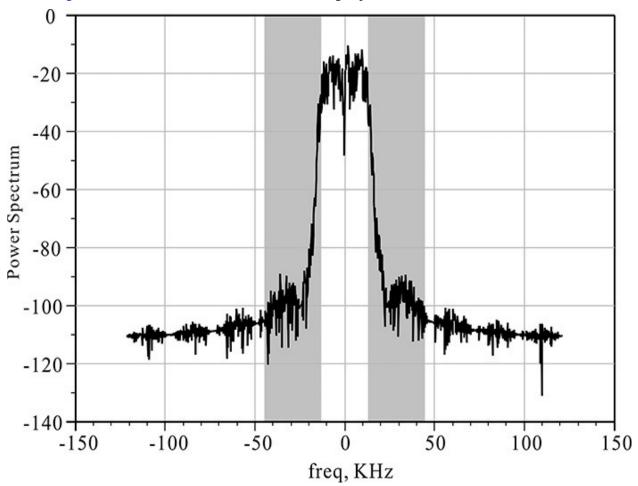

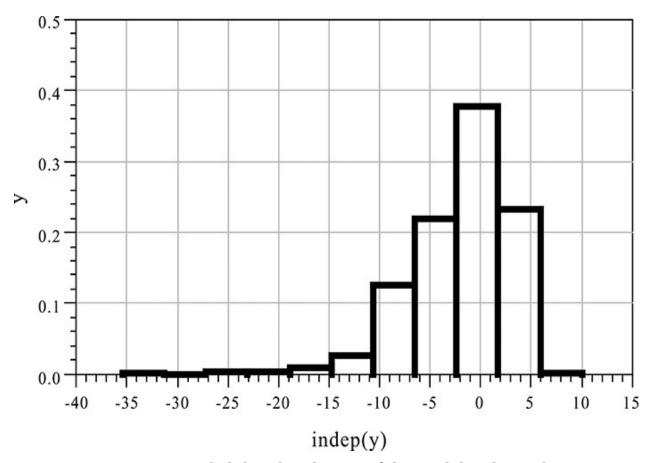

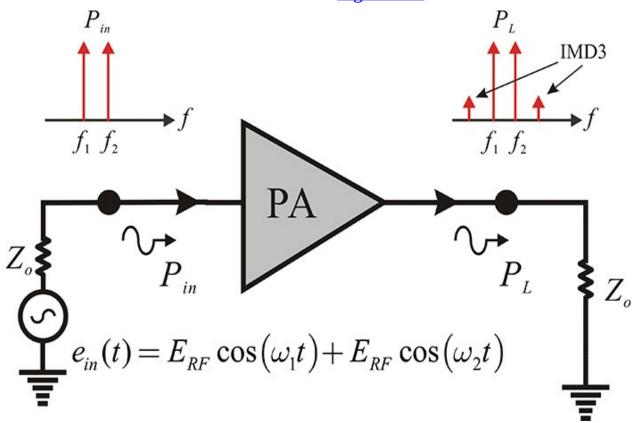

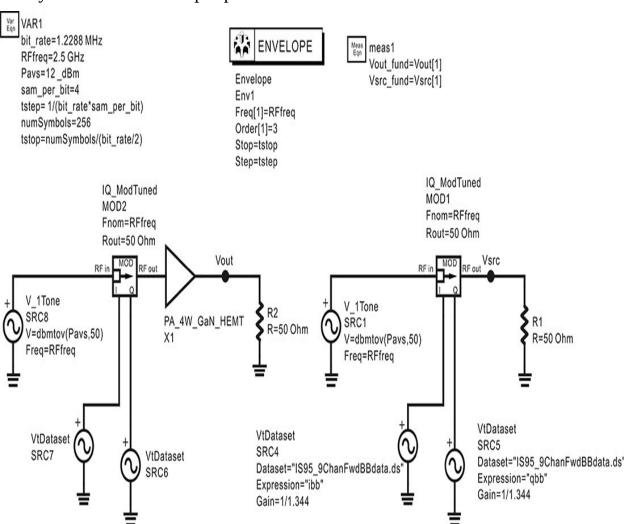

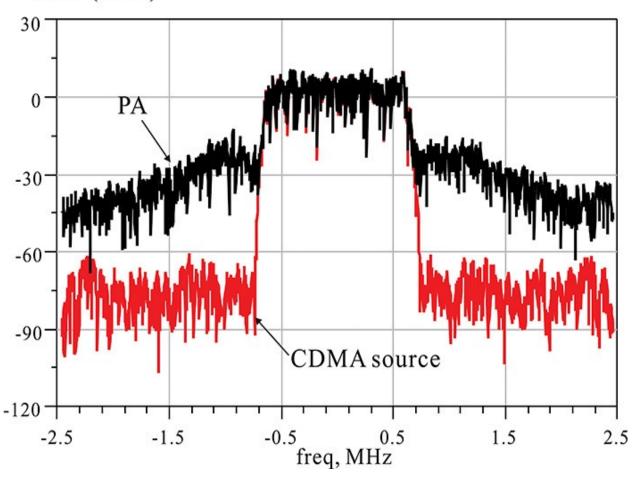

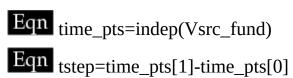

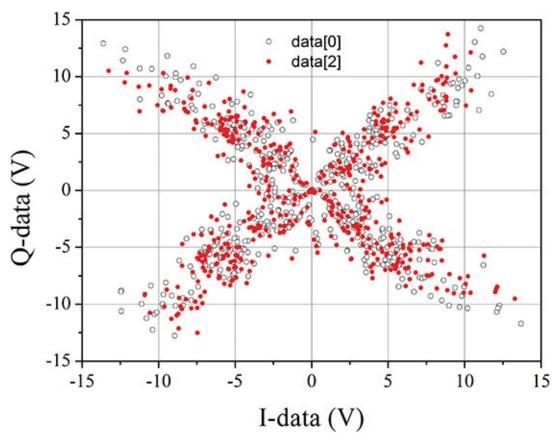

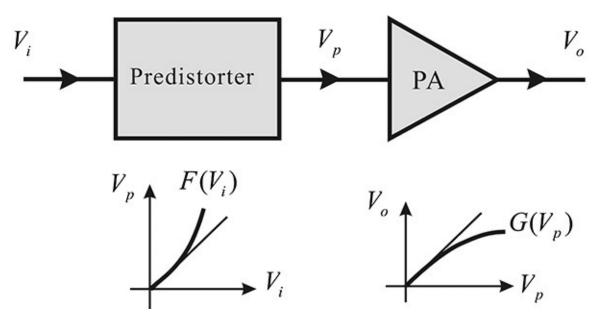

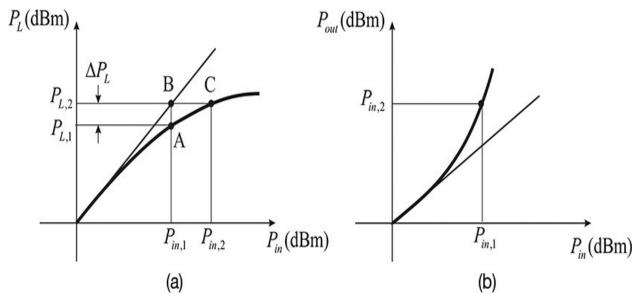

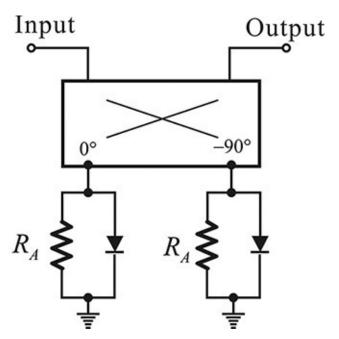

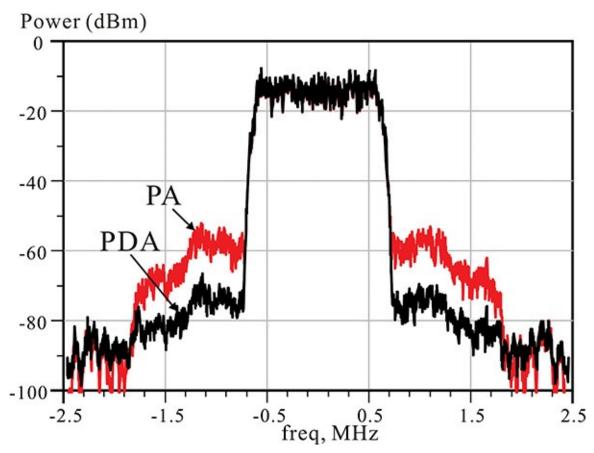

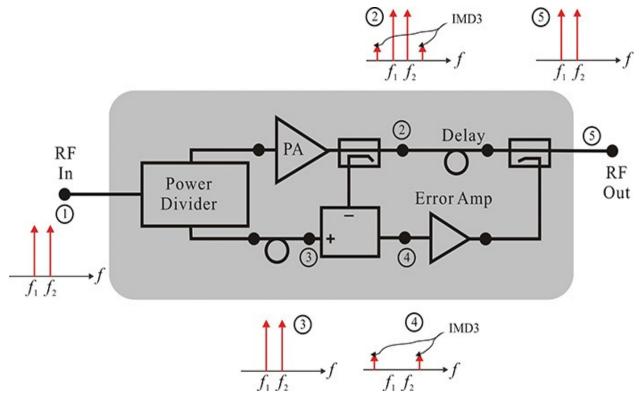

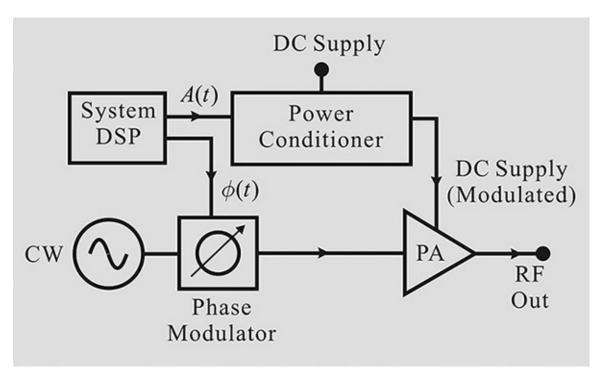

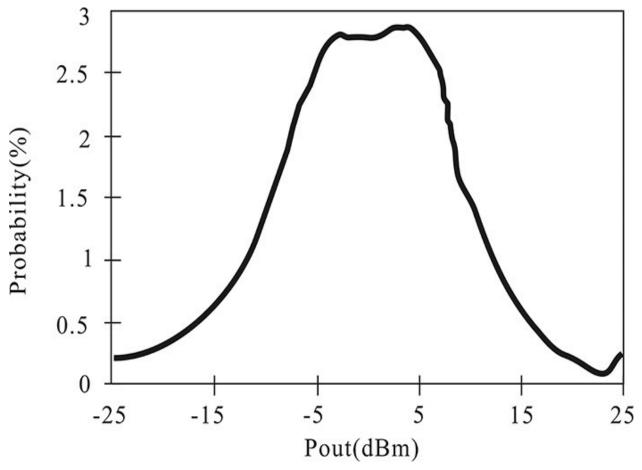

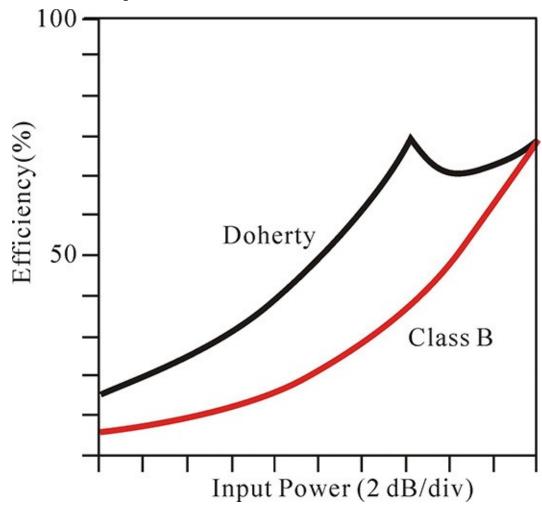

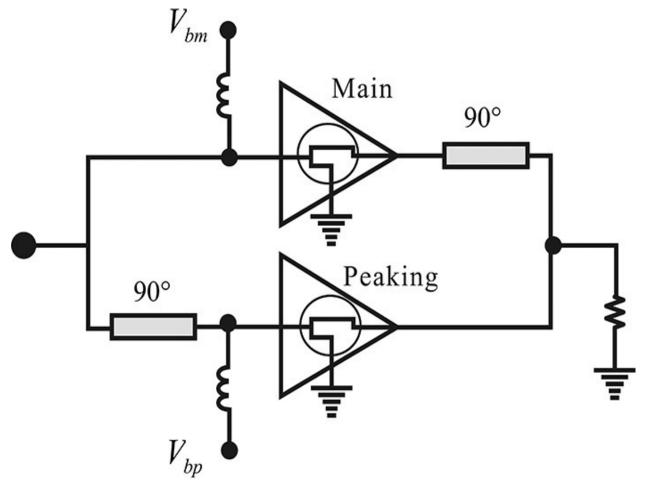

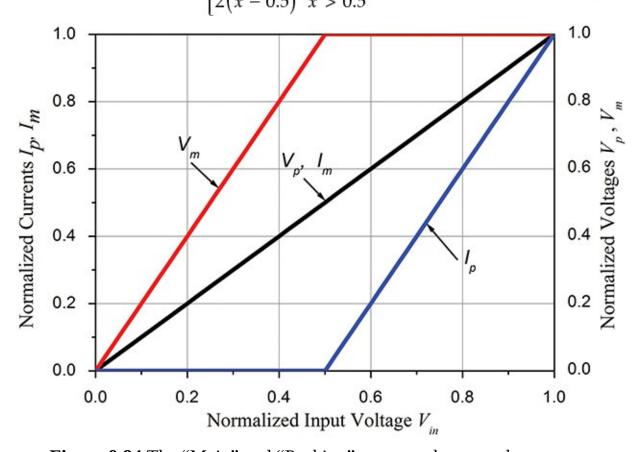

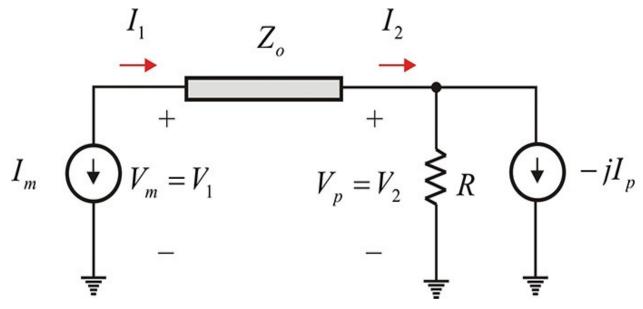

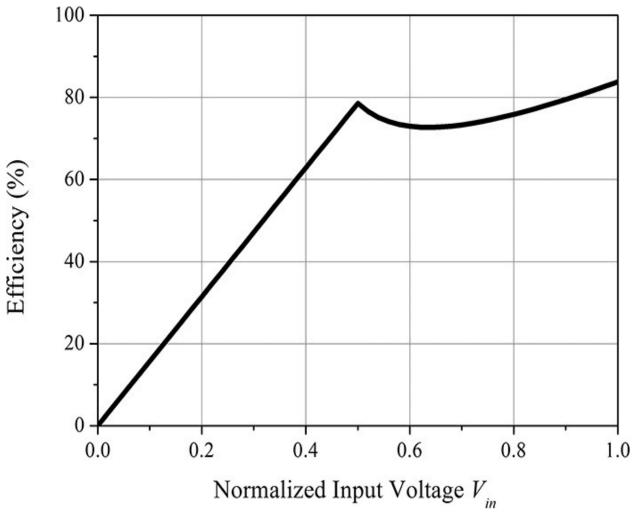

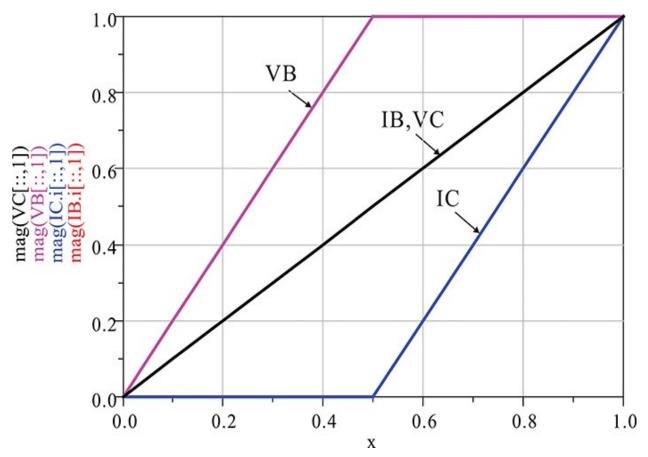

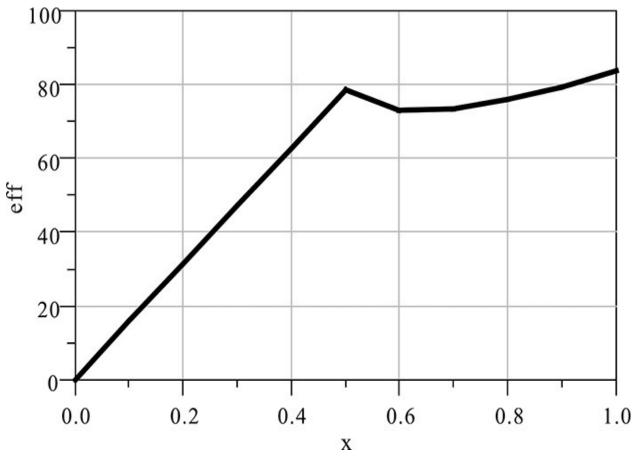

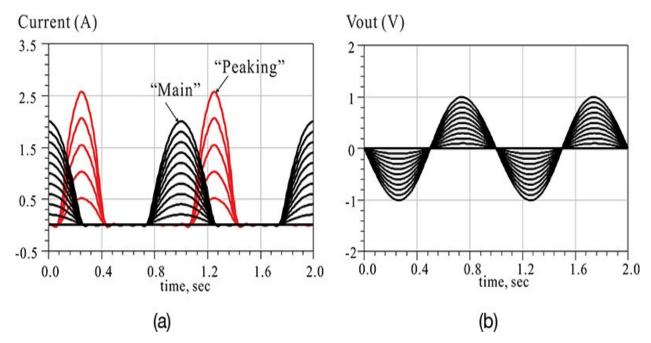

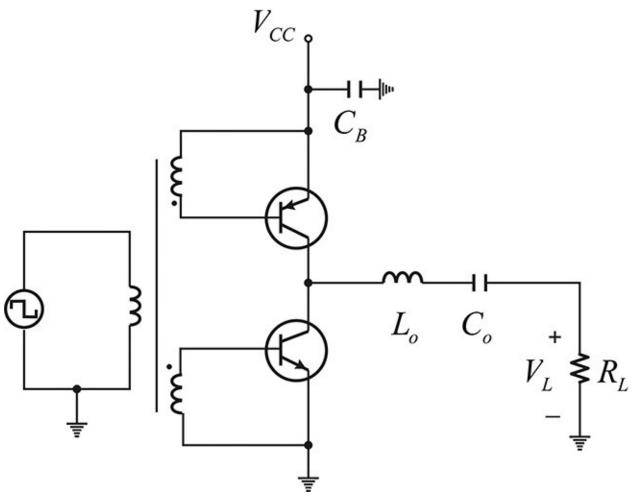

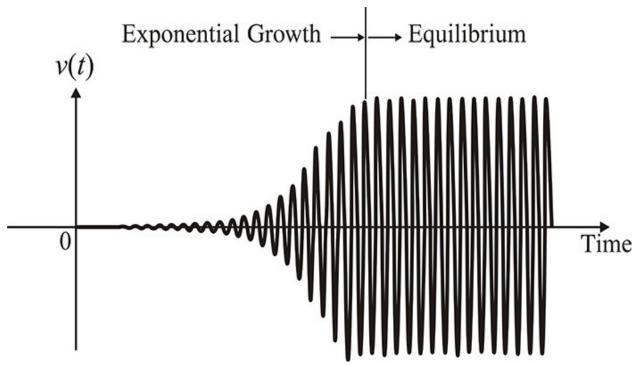

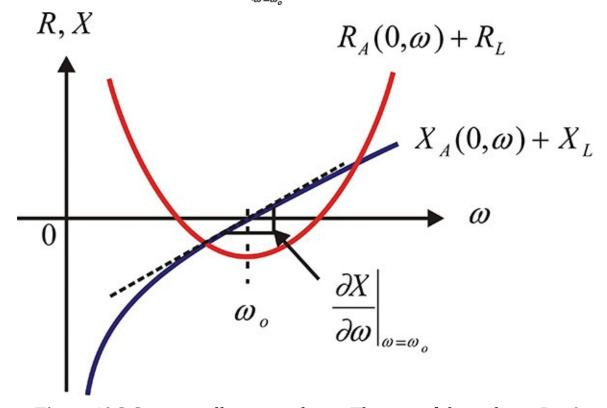

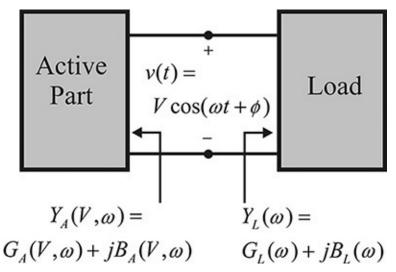

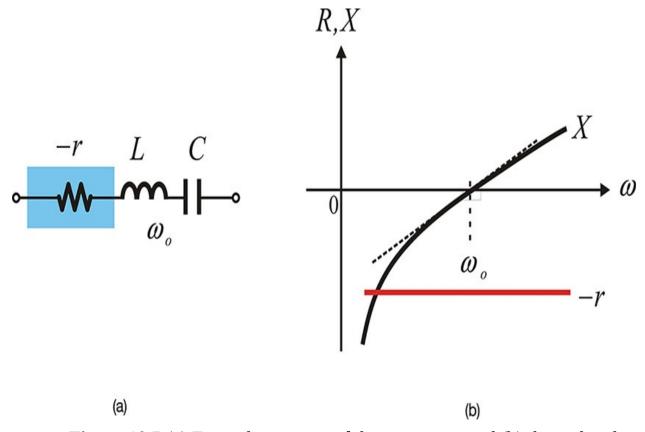

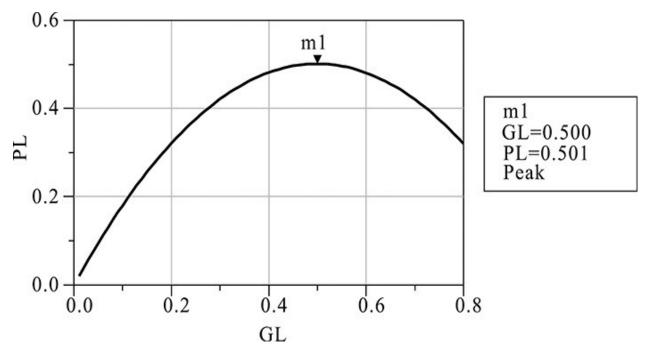

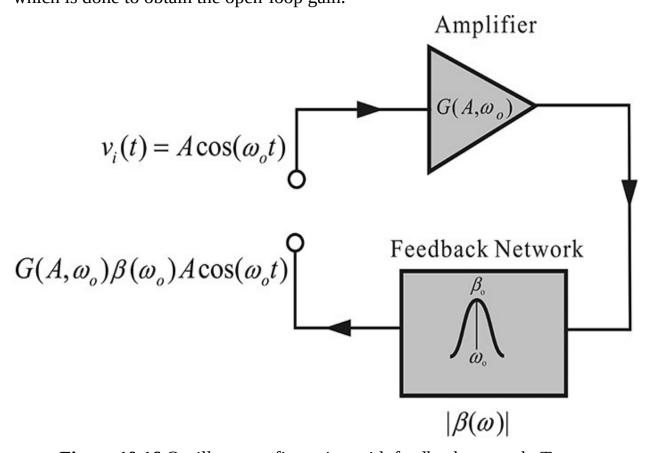

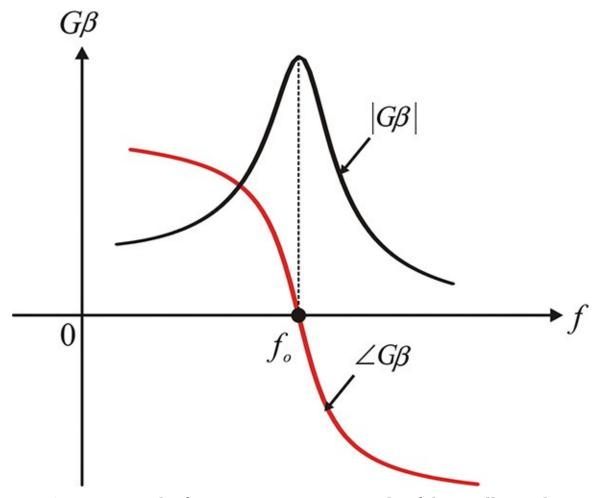

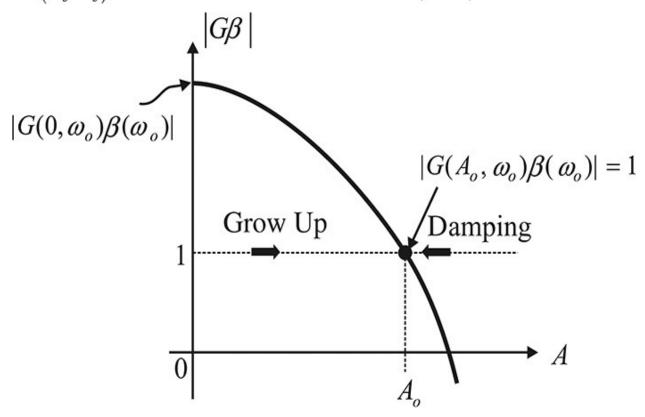

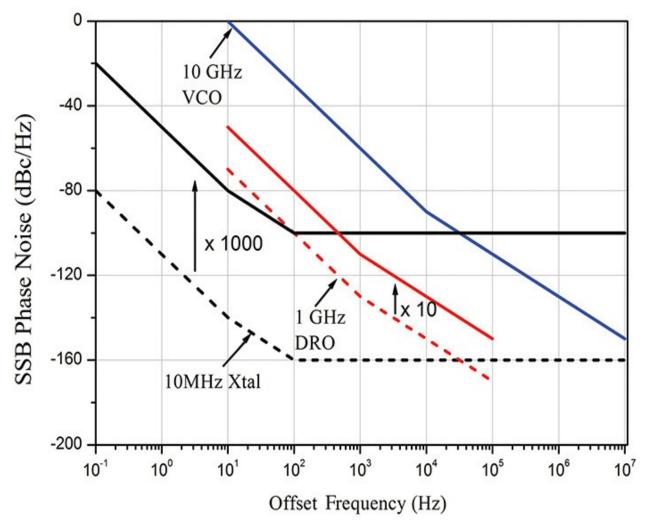

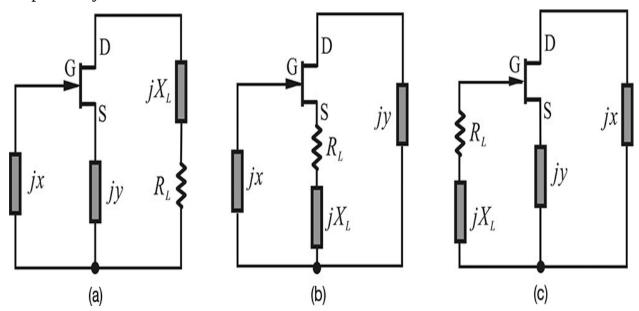

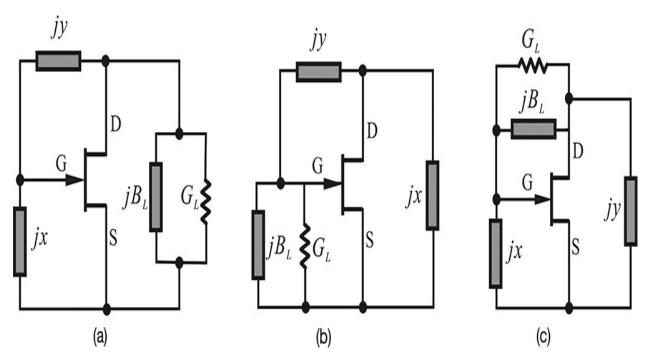

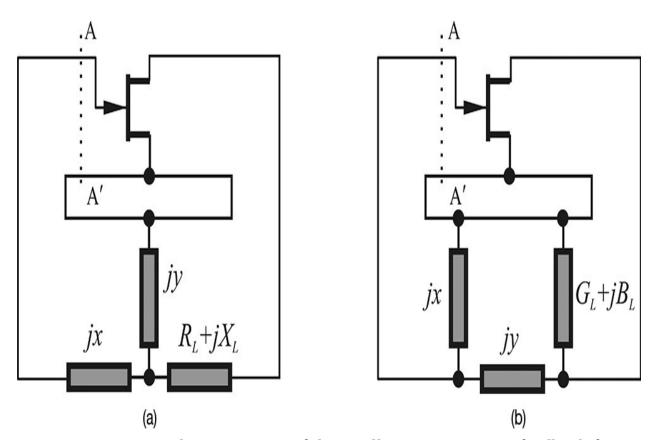

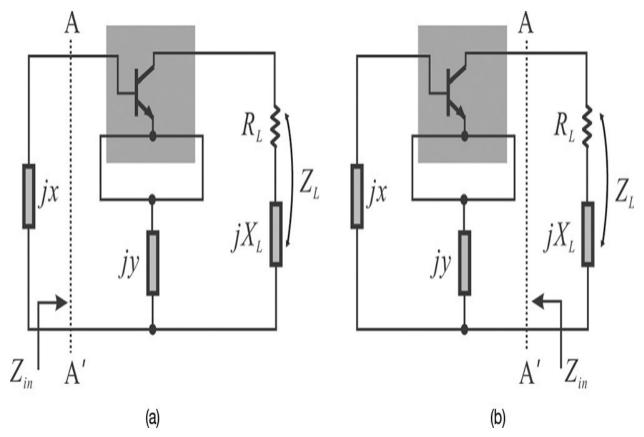

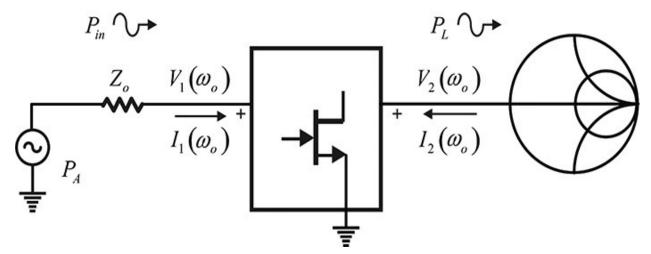

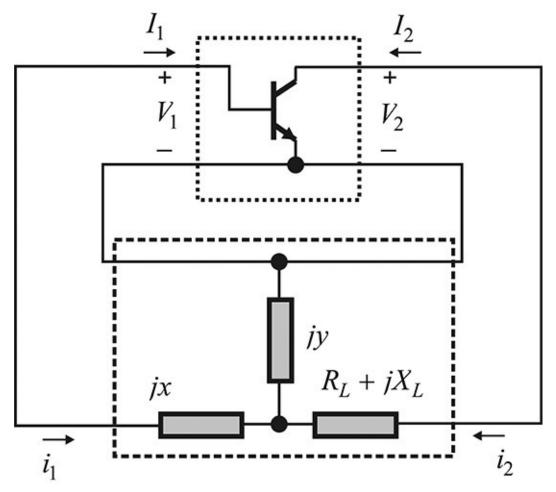

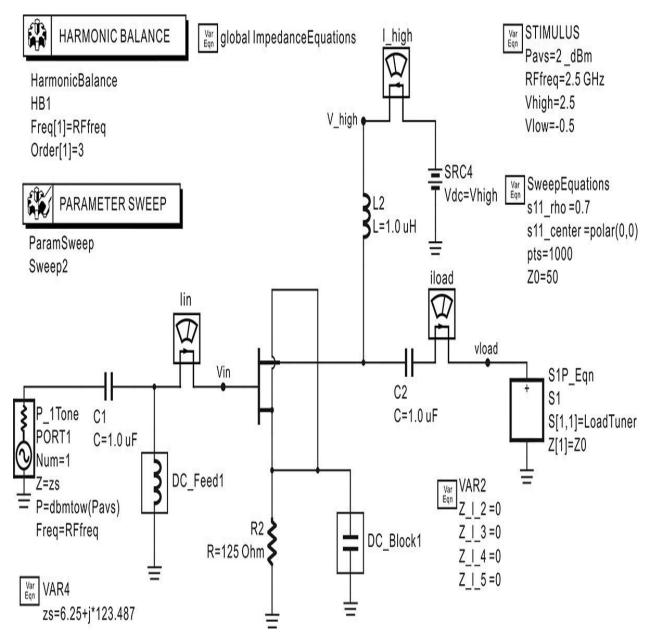

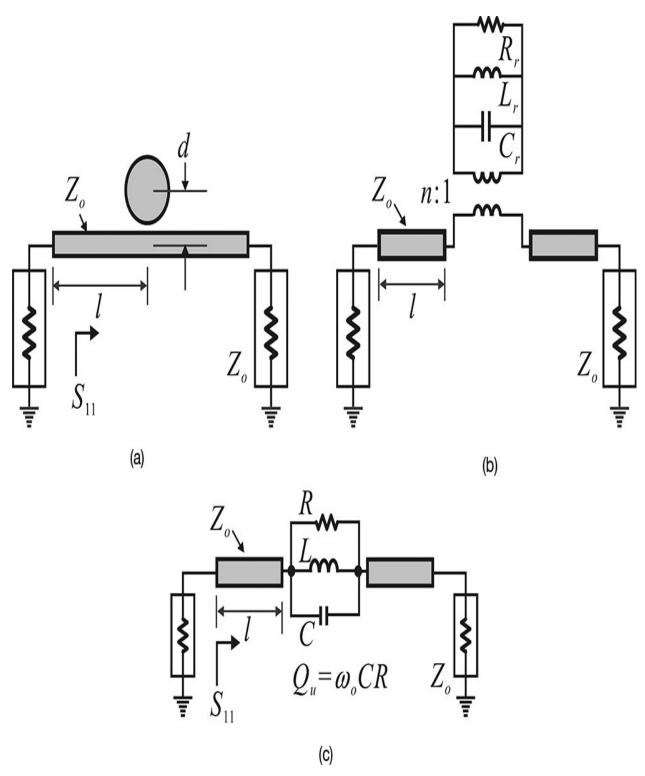

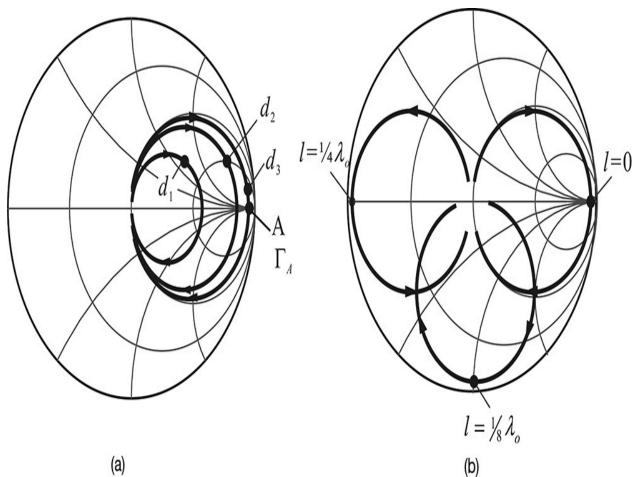

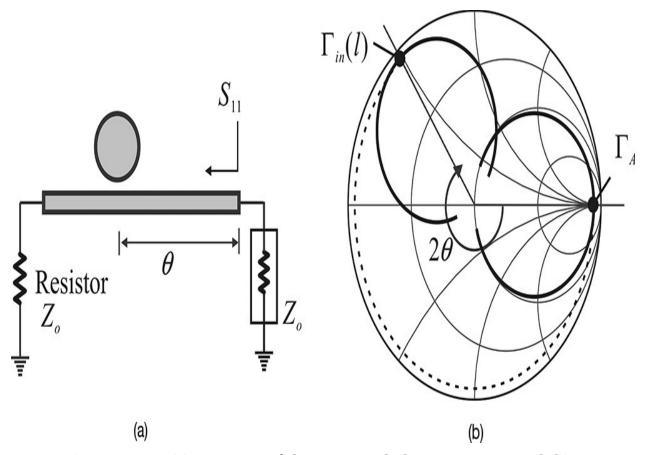

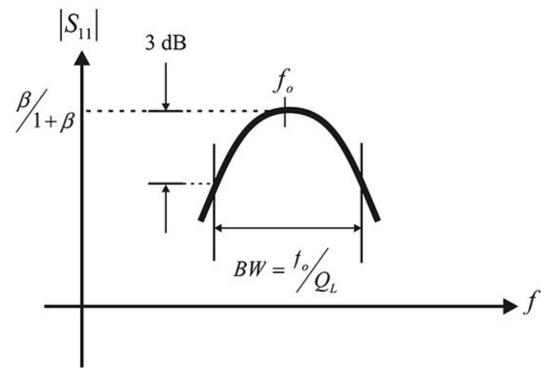

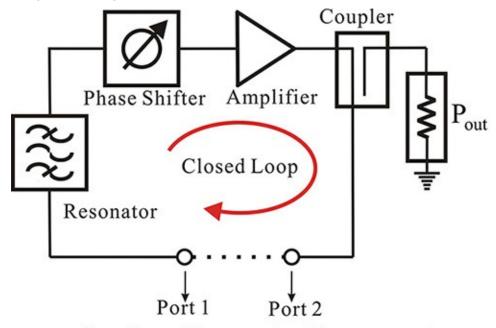

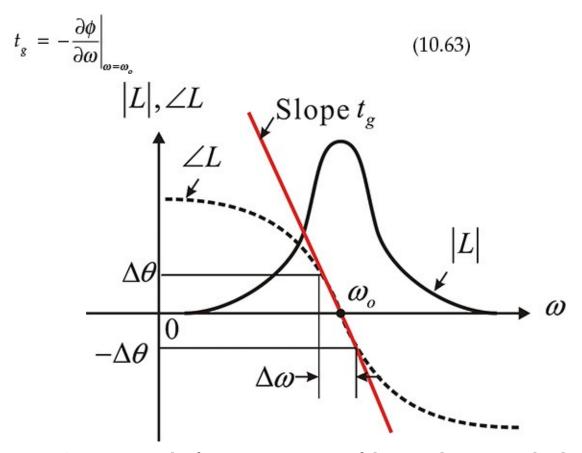

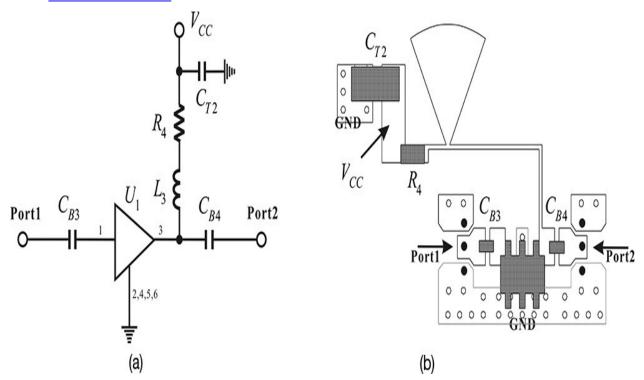

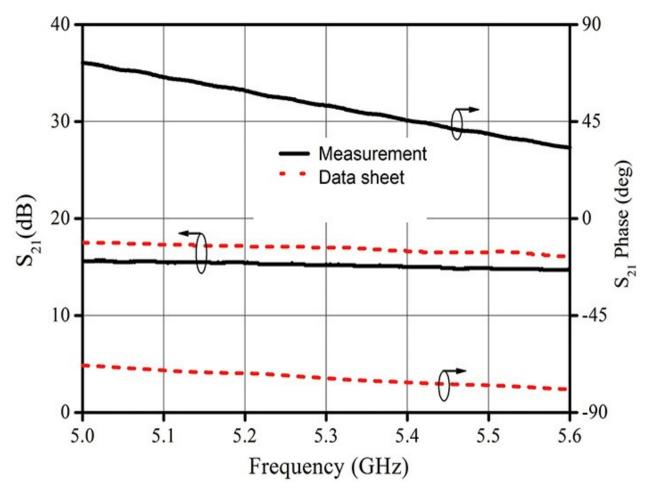

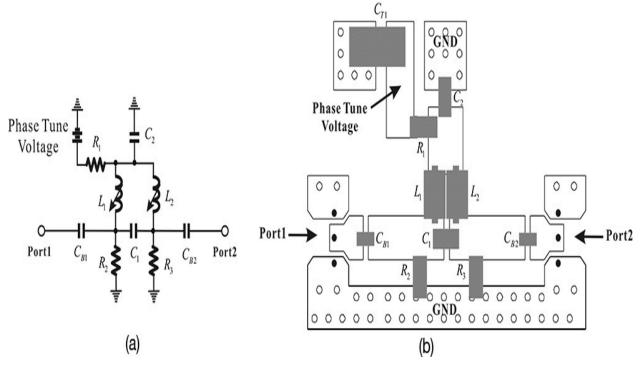

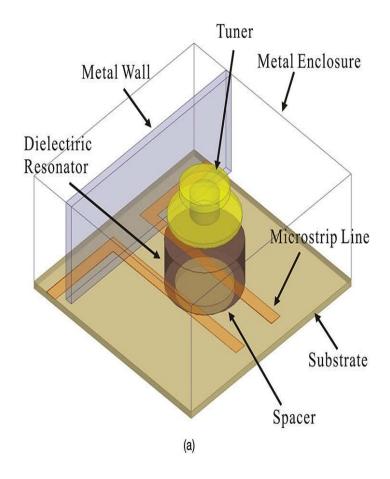

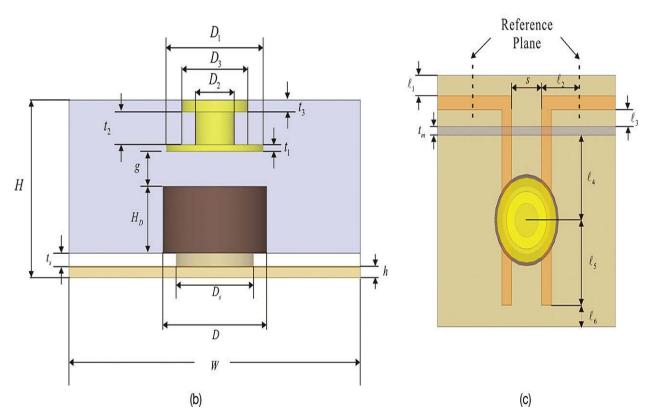

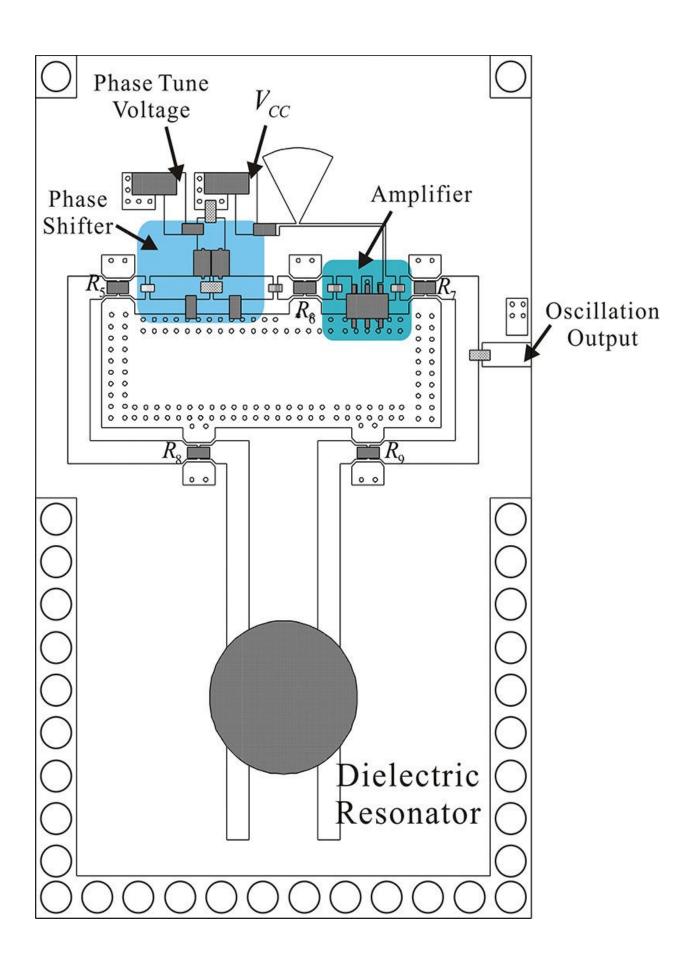

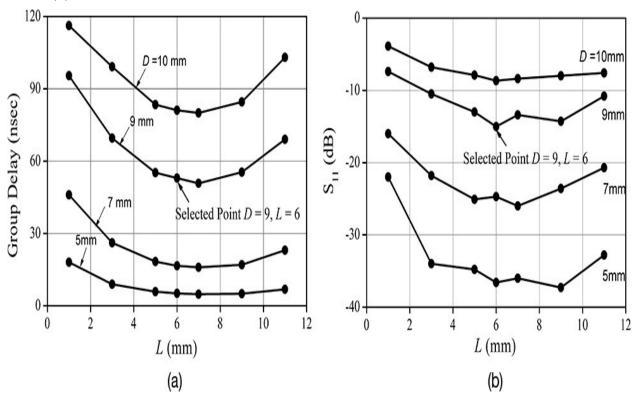

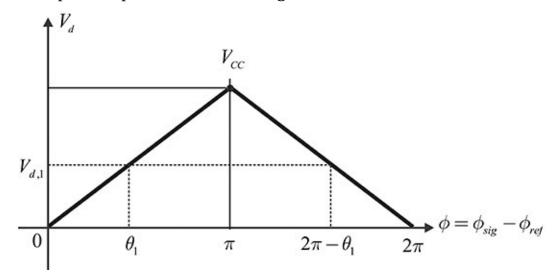

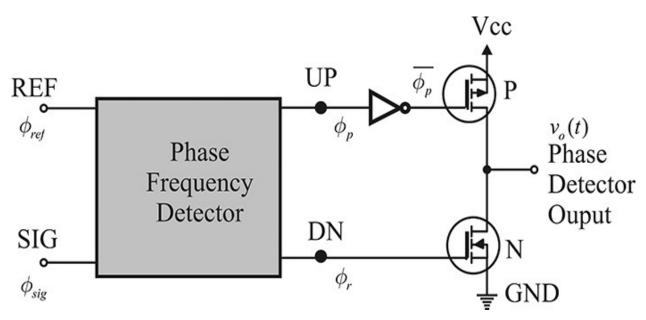

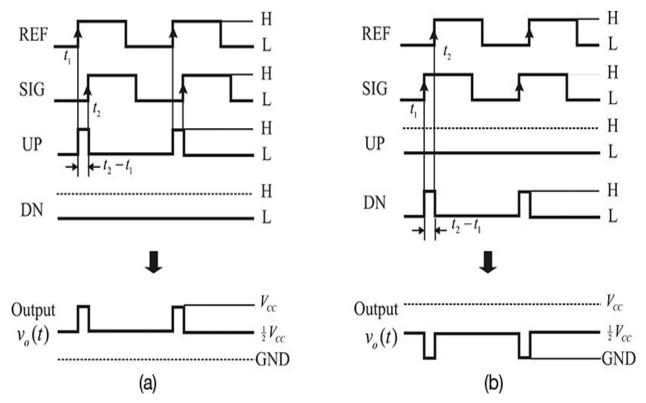

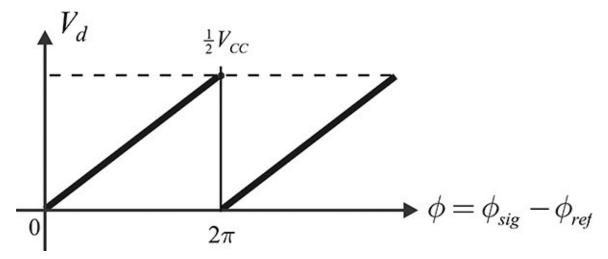

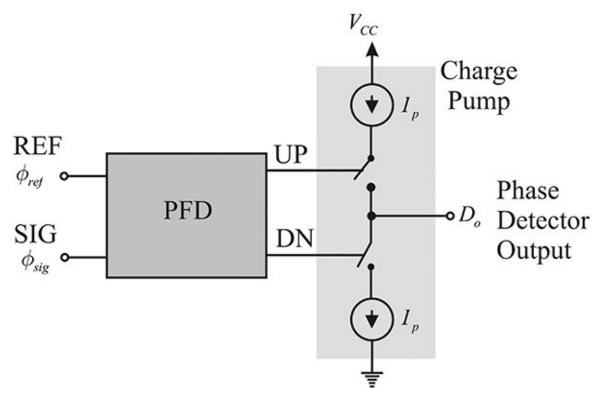

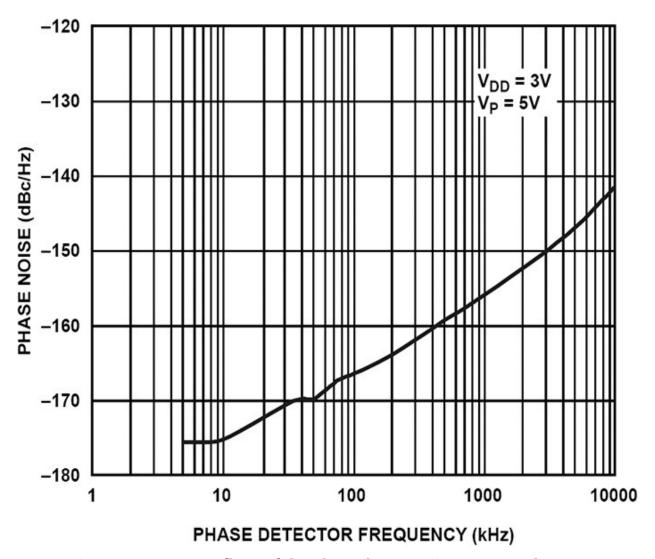

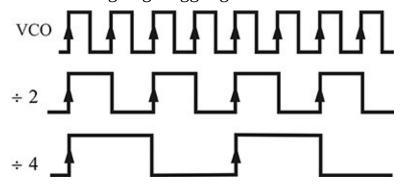

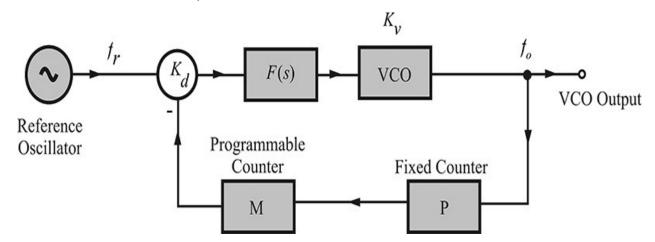

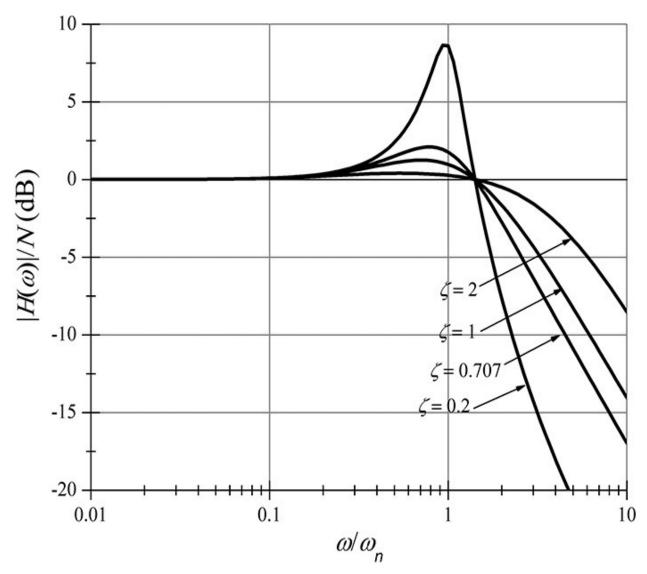

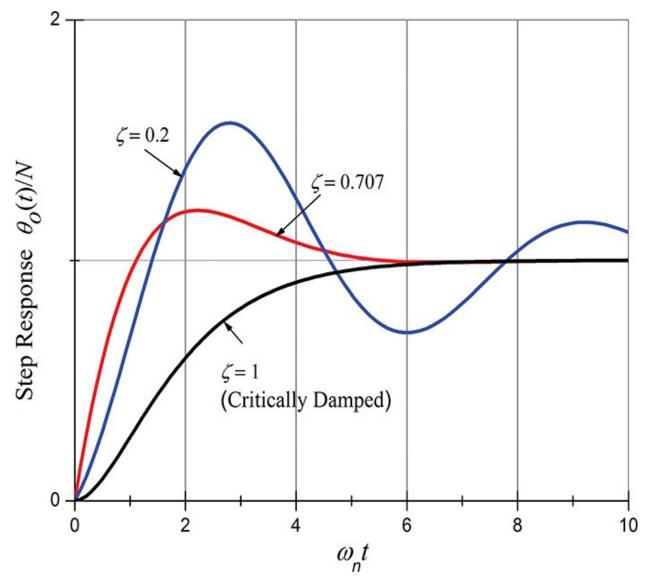

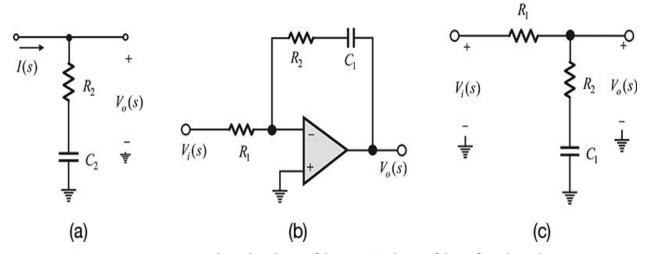

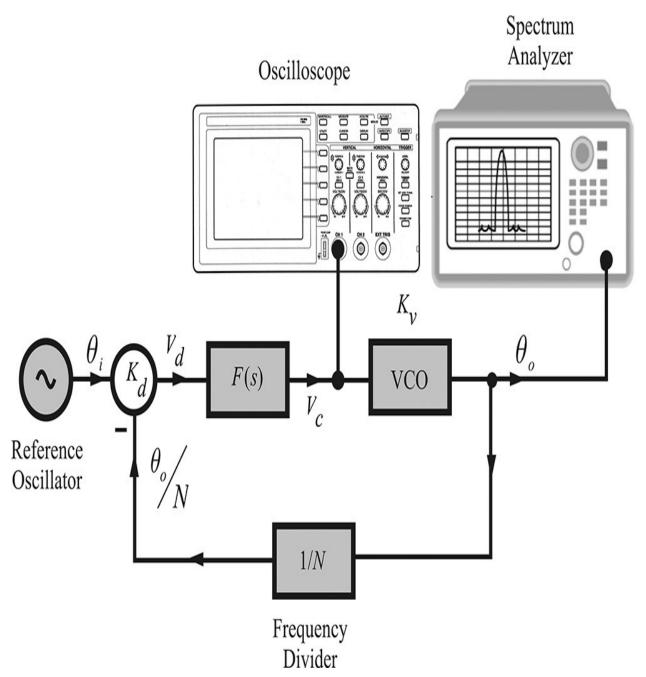

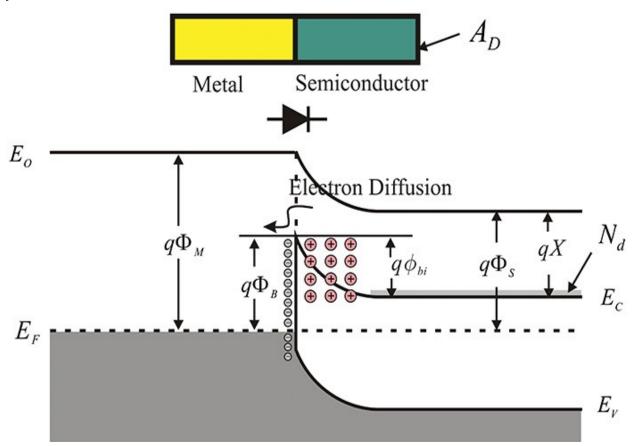

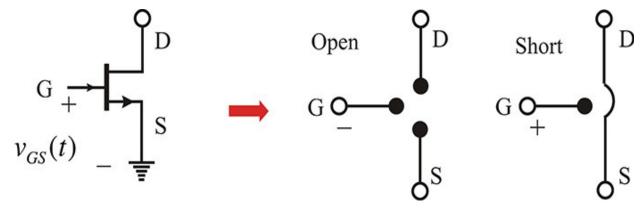

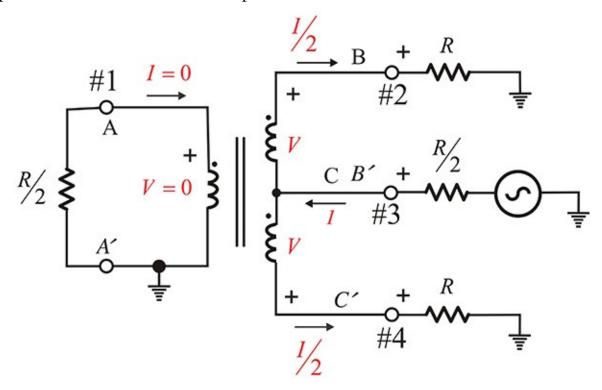

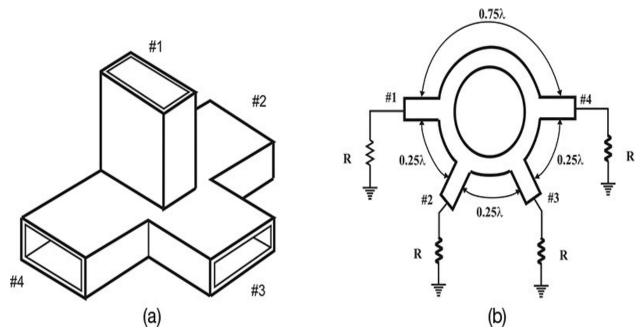

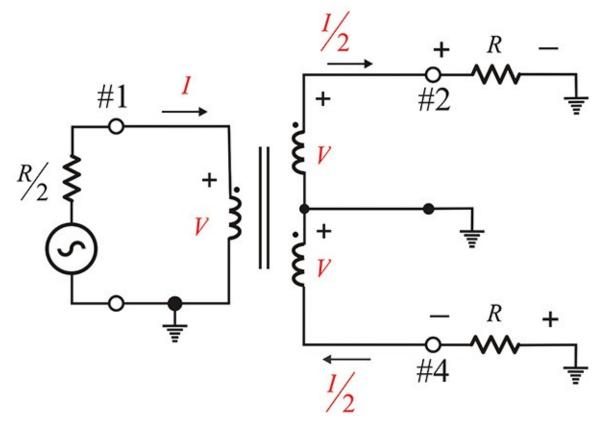

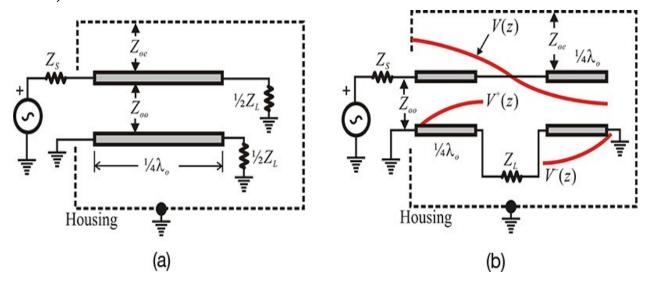

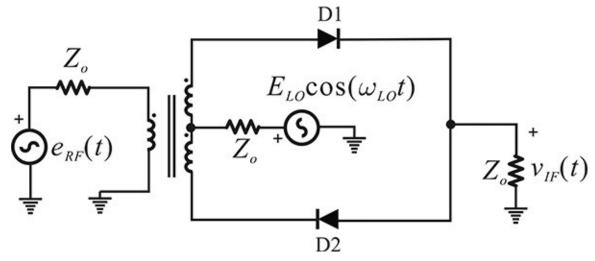

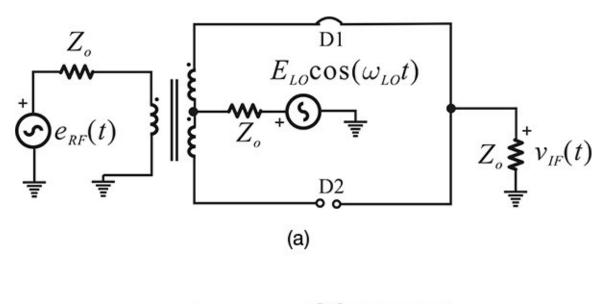

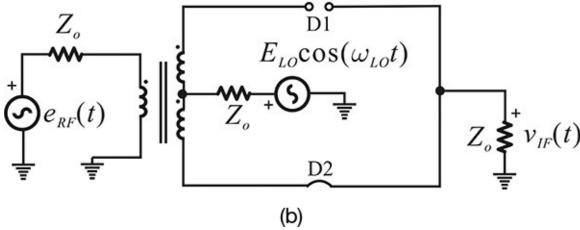

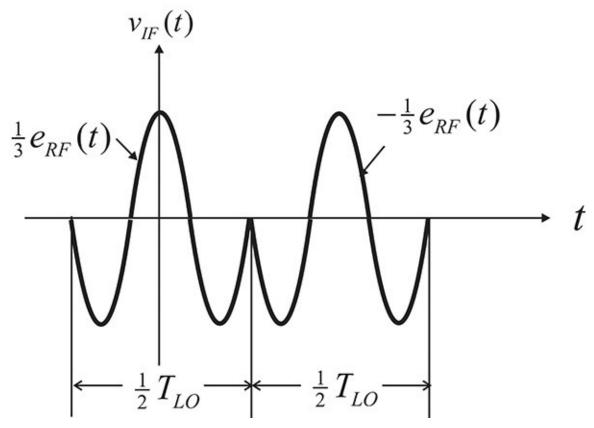

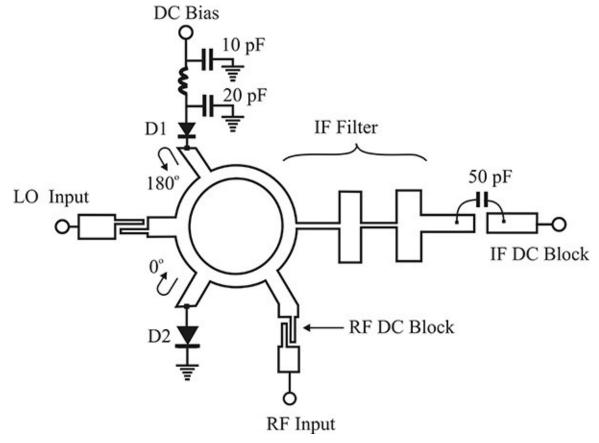

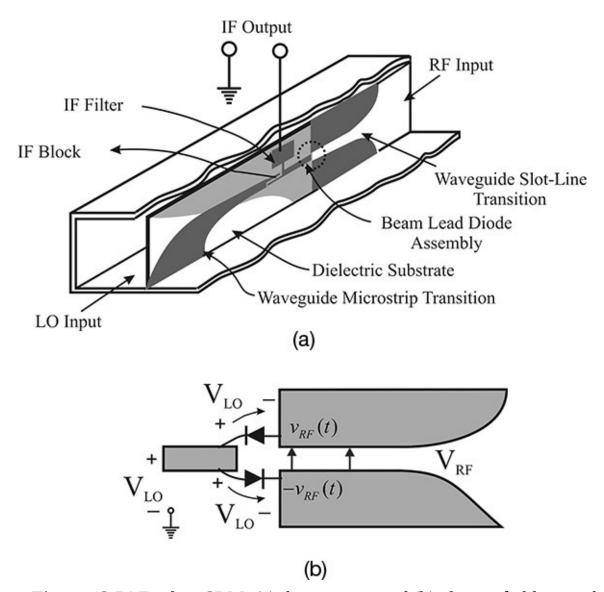

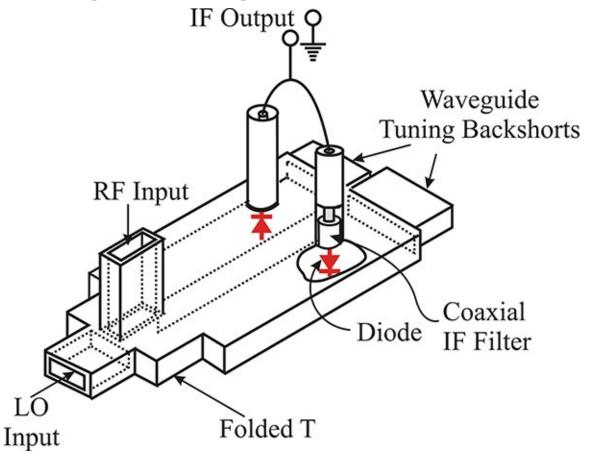

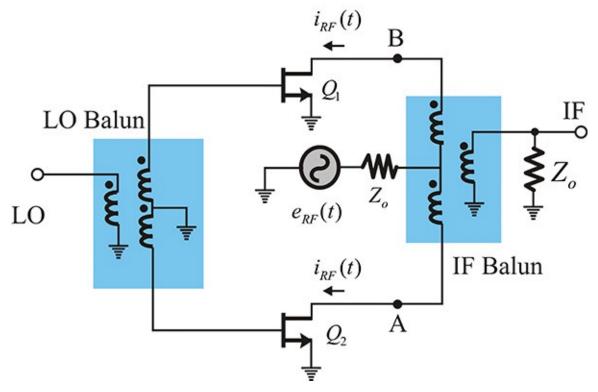

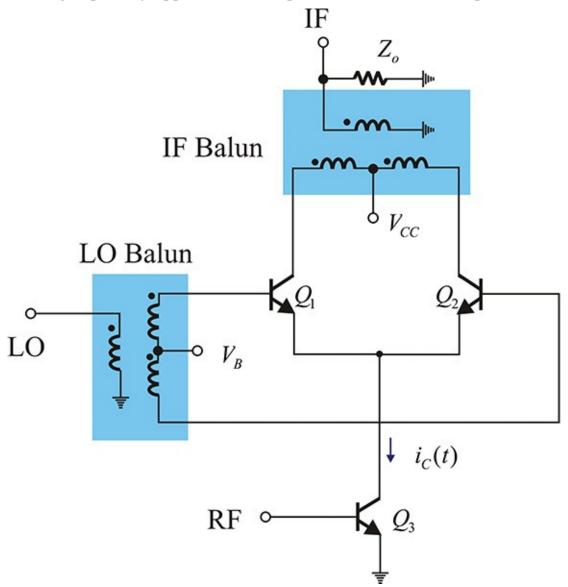

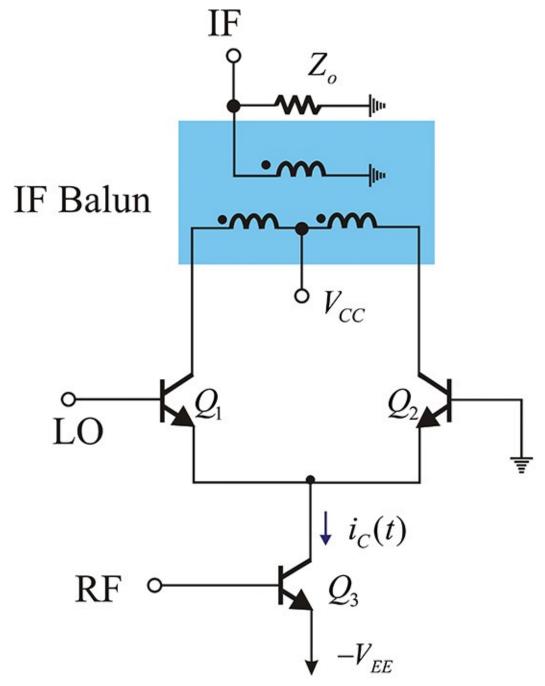

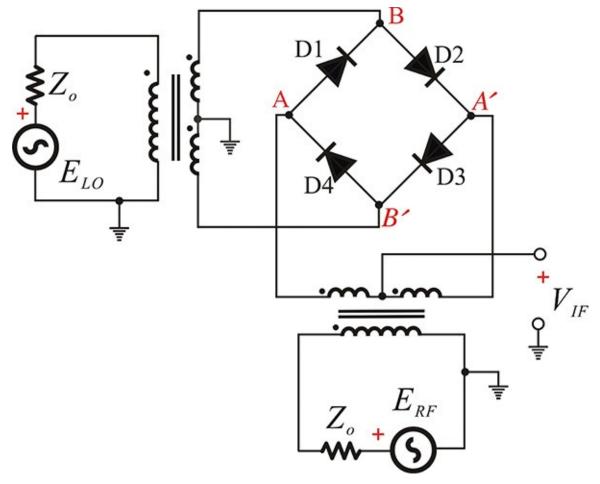

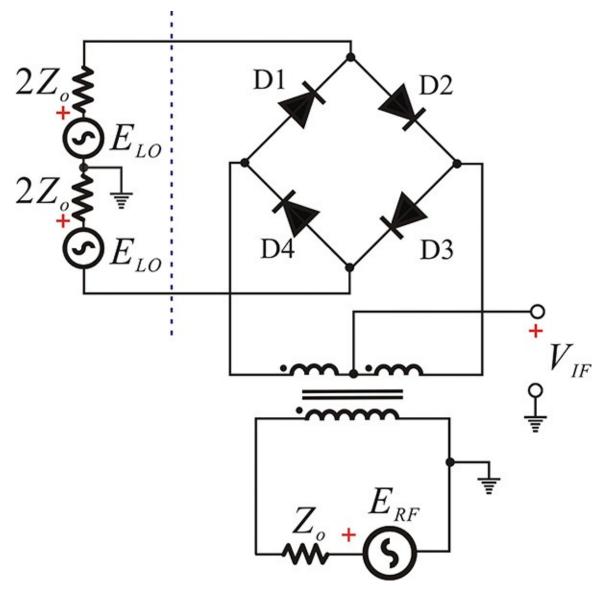

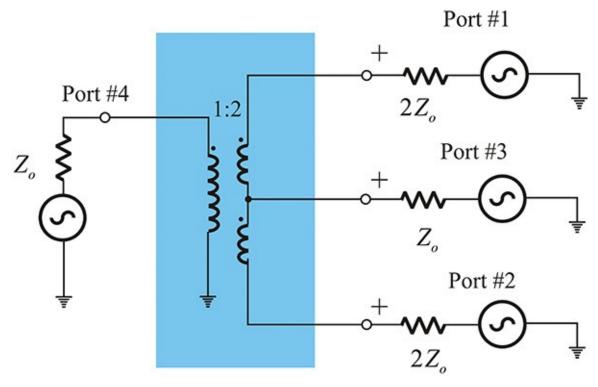

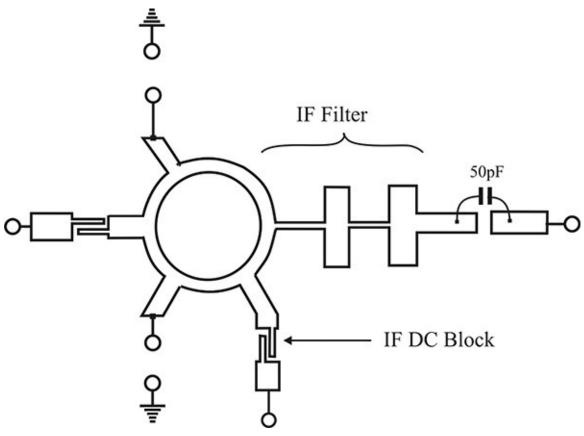

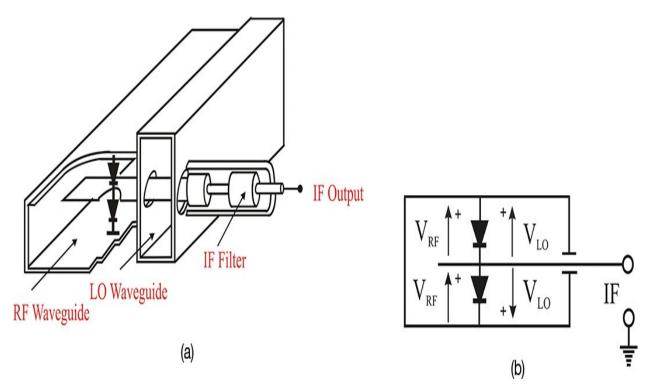

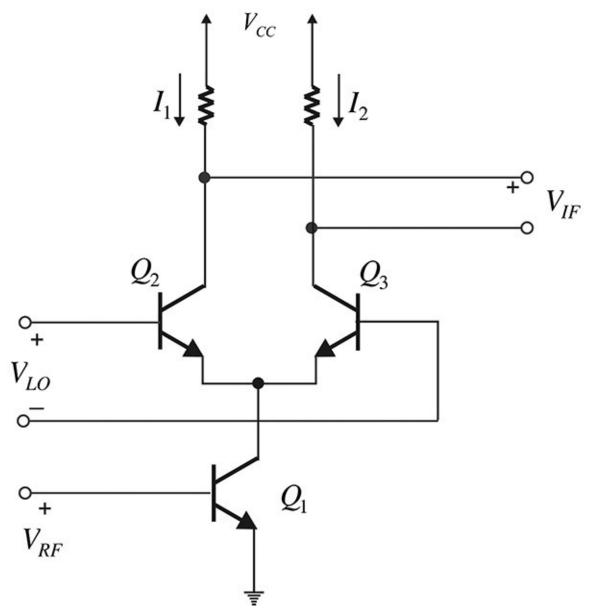

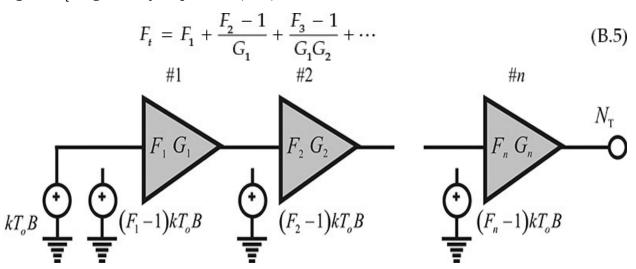

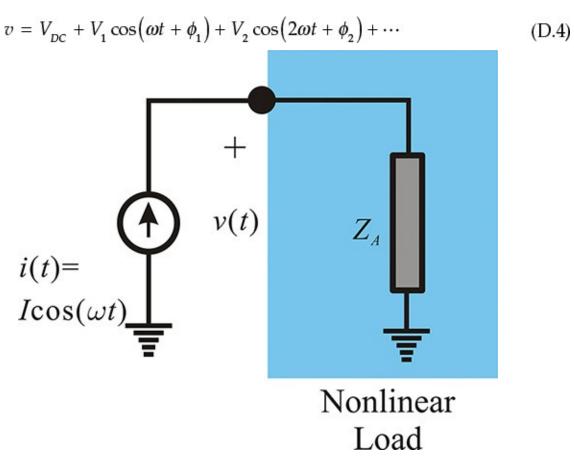

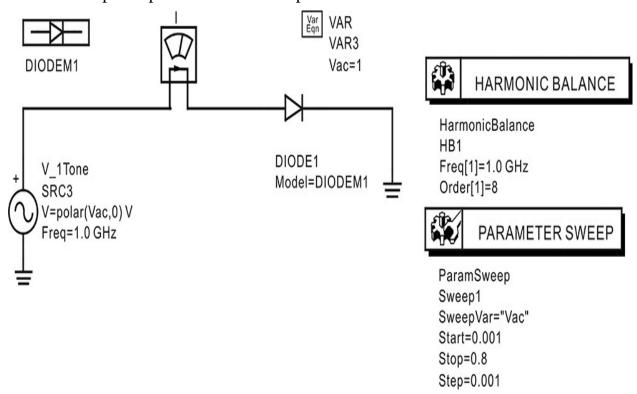

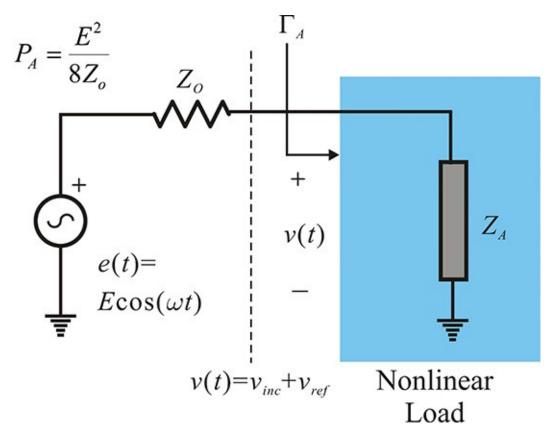

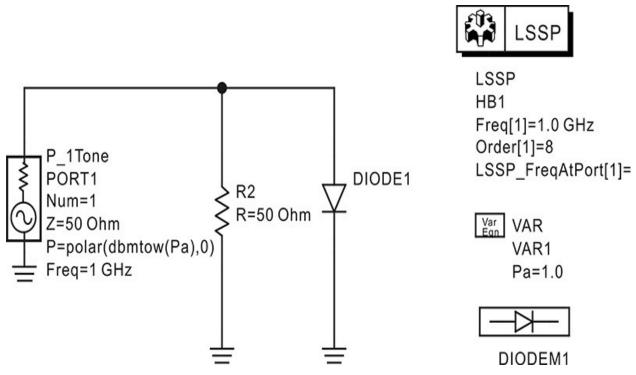

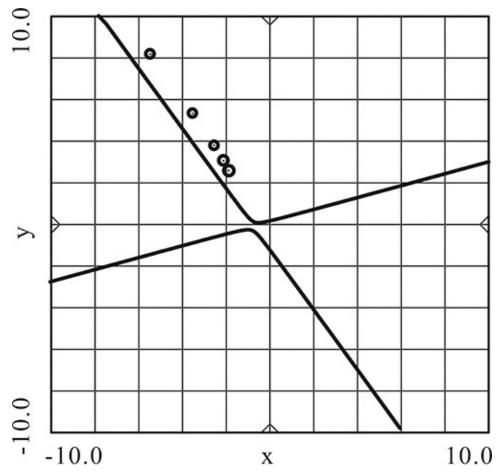

The limitations of the method presented will primarily be in the connector. Typical SMA connectors can be used up to 18 GHz. Thus, the measurement of impedance characteristics is possible only below 18 GHz using an SMA